组合逻辑中的2-4译码器

设计一个2-4译码器。

2-4译码器,输入的2位二进制代码共有四种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。由此可得如下表1-6的真值表。将输入的A、B和输出Y0、Y1、Y2、Y3的关系写成逻辑表达式则得到:

Y0=A’B’

Y1=A’B

Y2=AB’

Y3=AB

真值表

逻辑电路

1. 知识点

- 通过实验理解译码器电路;

- 学习Verilog HDL行为级描述方法描述组合逻辑电路。

2. 用CircuitJS仿真

2:4译码器在CircuitJS中的仿真效果

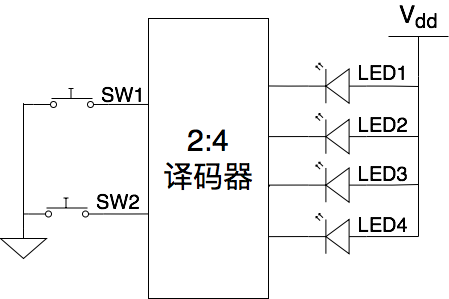

3. 原理图

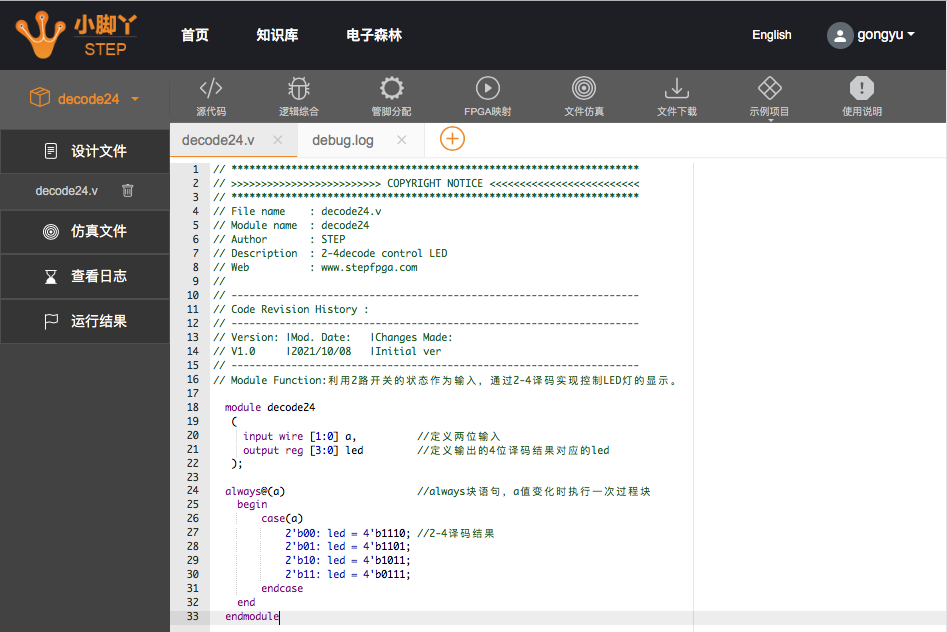

4. Verilog代码

// ******************************************************************** // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // ******************************************************************** // File name : decode24.v // Module name : decode24 // Author : STEP // Description : 2-4decode control LED // Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2021/10/08 |Initial ver // -------------------------------------------------------------------- // Module Function:利用2路开关的状态作为输入,通过2-4译码实现控制LED灯的显示。 module decode24 ( input wire [1:0] a, //定义两位输入 output reg [3:0] led //定义输出的4位译码结果对应的led ); always@(a) //always块语句,a值变化时执行一次过程块 begin case(a) 2'b00: led = 4'b1110; //2-4译码结果 2'b01: led = 4'b1101; 2'b10: led = 4'b1011; 2'b11: led = 4'b0111; endcase end endmodule

2:4译码器在Web IDE中的代码界面

5. 管脚分配

6. 功能验证

- 打开Lattice Diamond,建立工程。

- 新建Verilog HDL设计文件,并键入设计代码。

- 综合并分配管脚,将输入信号a[0]、a[1]分配至拨码开关,将输出信号led[0]~led[3]分配至板卡上的LED。a[0]/M7,a[1]/M8,led[0]/N13,led[1]/M12,led[2]/P12,led[3]/M11

- 构建并输出编程文件,烧写至FPGA的Flash之中。

- 按下对应按键/拨动拨码开关,观察输出结果。