7段数码管显示

硬件平台

设计要求

- 了解数码管显示的工作原理

- 掌握Verilog语言设计数码管显示驱动

- 掌握Verilog语言设计串行转并行逻辑

- 掌握数码管动态显示,按秒实现0到9循环左移显示

工作原理

八段数码管显示原理

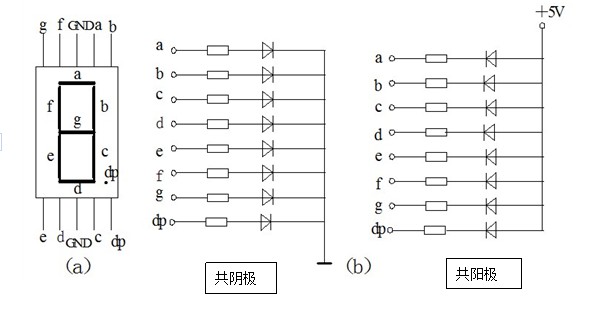

数码管是工程设计中使用很广的一种显示输出器件。一个8段数码管分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成。实际是由8个LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如下图所示:

图1 共阳极、共阴极数码管

共阴8段数码管的信号端低电平有效,而共阳端接高电平有效。当共阳端接高电平时只要在各个位段上加上相应的低电平信号就可以使相应的位段发光。比如:要使a段发光,则在a段信号端加上低电平即可。共阴极的数码管则相反。

数码管有两种显示方式:

- 一种是独立显示模式,由上图可知,控制数码管显示我们需要8根数据信号线和1根控制端选通信号线,这样如果我们需要4位数码管就需要4*9 = 36根信号线才能分别显示。独立显示模式实现简单,但是需要大量的信号线。

- 另一种是扫描显示模式,即所有数码管共用8根数据信号线,各自再有1根选通信号线,采用分时的方式循环选通各位数码管,这样就需要8+4 = 12根信号线进行显示。利用人眼的“视觉暂留效应”,可以使数码管显示看起来是同时显示。扫描显示模式实现复杂,但是节约信号线的使用。

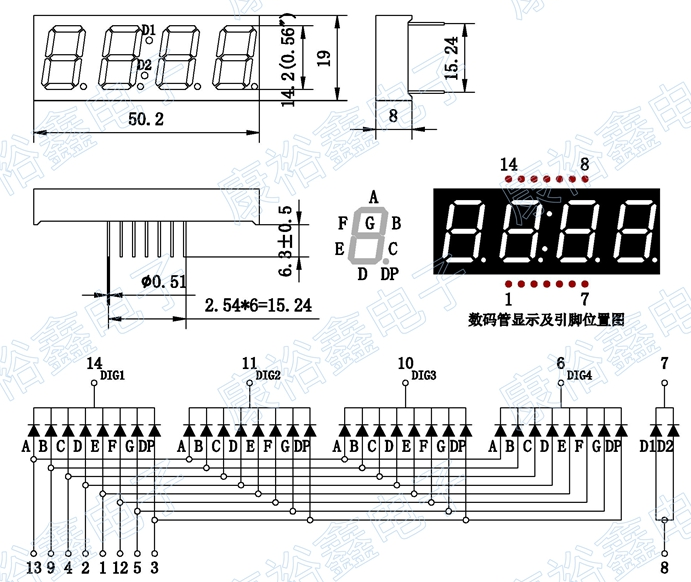

在STEP-Baseboard上的4位数码管结构如下:

图2 数码管结构

因数码管上的4位需要显示不同的数字,故我们需要扫描的方式, 扫描模式采用分时的方式循环选通各个数码管,依次显示第1、第2、第3、第4位,利用人眼睛的视觉暂留效应,扫描的频率越高,数码管显示循环周期越小,当扫描频率足够高(例如当扫描频率等于100Hz)时,则在人眼看到的数码管显示就是连续的。

当扫描频率 = 100Hz,则4位数码管单次扫描周期为10ms,因为4位数码管分时显示,则每位数码管闪烁时间应为2.5ms。

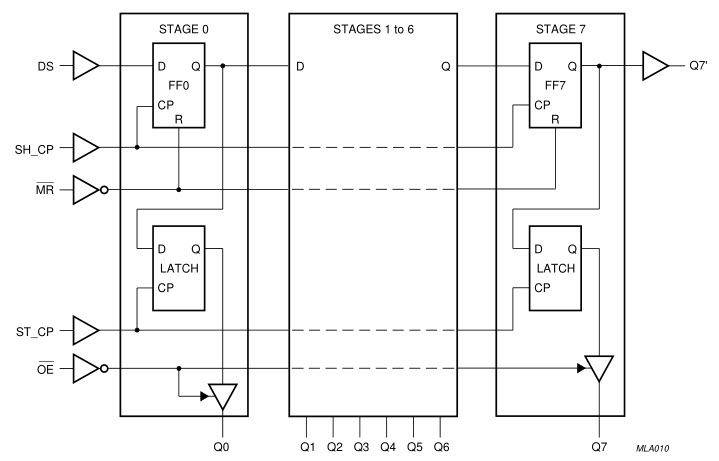

74HC595驱动原理

从前面我们知道驱动一个4位数码管至少需要12根线,对于小脚丫FPGA的引脚资源来说还是很紧张的。因此在STEP-Baseboard实验平台上采用了74HC595来驱动数码管显示,这样可以有效的节约我们的管脚资源。 74HC595是较为常用的串行转并行的芯片,包括一个8位移位寄存器和一个存储器,三态缓冲输出。在最简单的情况下我们只需要控制3根引脚输入得到8根引脚并行输出信号。

图5 74hc595引脚功能

图6 74hc595逻辑图

图7 74hc595时序图

一个4位数码管至少需要12根信号线控制显示,因此STEP-Baseboard上采用了两片74HC595级联来实现控制。单个74HC595芯片8根并行输出信号更新一次需要8个SHCP信号周期的时间长度,所以需要16个SHCP信号周期才能完成一位数码管的显示;

假如我们把每位数码管延时时间设为2.5ms(正好满足人眼暂留效应,看起来像是4位同时显示),对应16个SHCP信号周期,则SHCP信号周期应该为2.5ms/16 ≈ 156us,SHCP信号的频率应该为1000000us/156us ≈ 6.4KHz,这样在程序设计的时候我们可以将SHCP的控制信号(sclk_out)设置为6.4KHz左右。

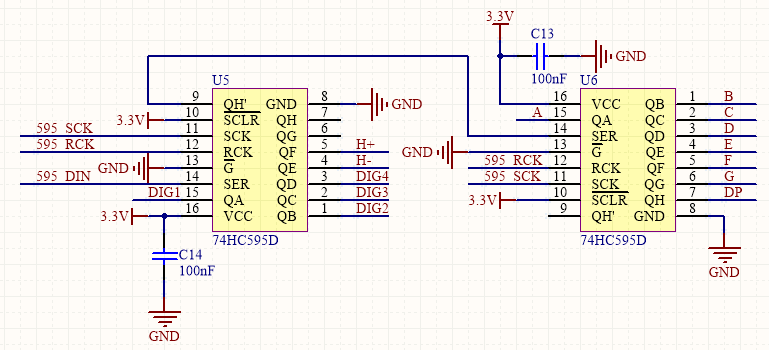

硬件连接

根据上面STEP-Baseboard采用的4为数码馆结构图可以看到,加上数码管中间的冒号显示,我们需要14根信号线控制。通过两片74HC595级联驱动实现了3根串行总线控制16根并行总线输出,有效减少了引脚需求。具体硬件连接如下所述:

FPGA的系统时钟来自于小脚丫FPGA开发板配置的25MHz时钟晶振,连接FPGA的C1引脚。

数码管模块电路原理图连接和八段共阴极数码管的结构分别如图所示:

图3 74HC595电路连接

图4 数码管电路连接

数码管模块、小脚丫与FPGA的引脚连接关系如下:

| 74HC595管脚 | 11(SCK) | 12(RCK) | 14(SER) |

|---|---|---|---|

| 小脚丫管脚 | 32 | 31 | 30 |

| FPGA管脚 | N2 | M1 | K1 |

代码设计

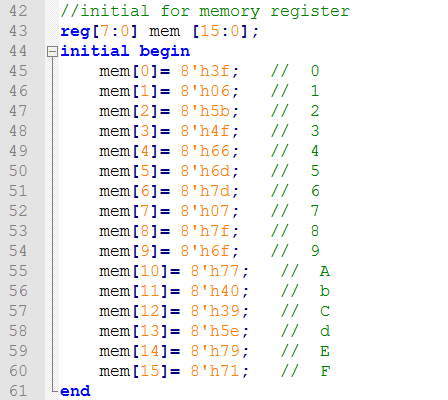

数码管是针对数字的显示器件,显示内容相对固定,我们首先把需要显示的内容定义为存储器,这样当我们需要显示时,只需要有存储器的地址就可以调用数据。

我们的数码管是由芯片74HC595驱动的,根据上面计算,SHCP的频率为6.4KHz,所以我们首先分频产生一个6.4KHz左右的信号clkdiv,然后再基于这个信号产生74HC595的控制时序。

小脚丫开发板晶振为25MHz,我们需要对时钟分频得到6.4KHz左右的信号,这样分频系数为25MHz/6.4KHz ≈ 3900。

parameter CLKDIVPERIOD=3900;

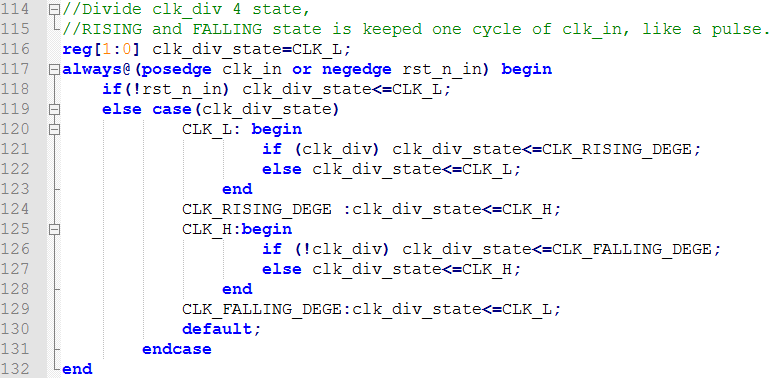

然后我们使用状态机将clk_div的高电平、低电平、上升沿和下降沿产生脉冲,方便我们后面结合上升沿和下降沿的状态完成74HC595的控制时序。

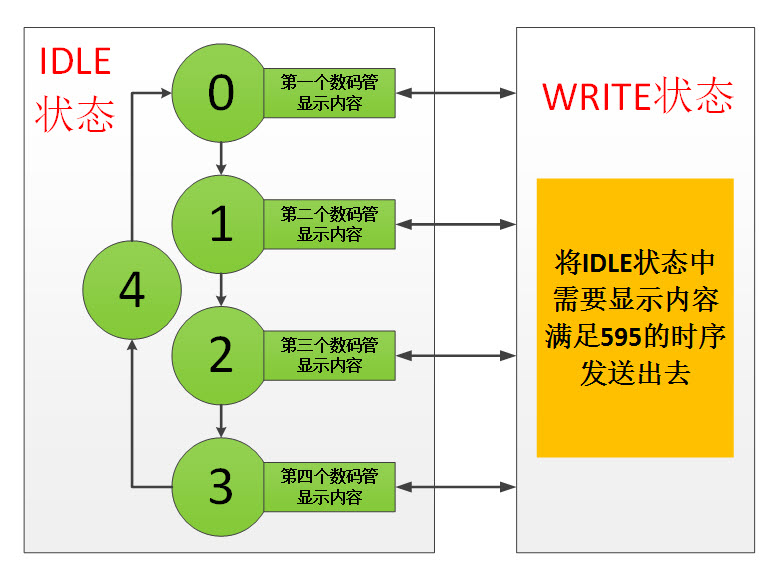

使用状态机我们将赋值和并行转串行分别完成,分为两个状态:

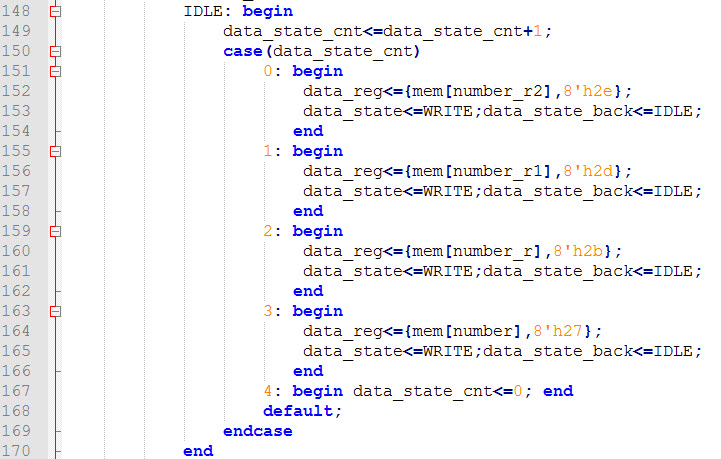

- IDLE状态:分时控制四位数码管各位需要显示的内容

- WRITE状态:实现74HC595的控制时序,将数码管需要显示的内容发送出去

- IDLE状态:分时显示的程序设计如下:

- WRITE状态:实现74HC595的控制时序,串行输出的程序设计如下:

如上所述就实现了数码管的分时显示,四位数码管可以同时显示不同的数字。

设计要求还需要按秒实现0到9循环左移显示,所以我们需要生成一个1Hz的信号clkdiv1Hz,然后由clkdiv1Hz触发完成显示内容的切换。

分频产生1Hz的时钟与上面产生6.4KHz信号的程序原理相同,这里不做赘述,然后基于1Hz时钟循环产生1~9的数据并使用寄存器逐级赋值锁存,方法如下:

引脚分配如下:

| 管脚名称 | clkin | rstnin | rclkout | sclkout | sdioout | |||

|---|---|---|---|---|---|

| FPGA管脚 | C1 | B1 | M1 | N2 | K1 |

系统运行

资源报告

| 资源 | 数量 | 比例 | 说明 |

|---|---|---|---|

| LUTs | 134 | 10% | |

| 寄存器 | 88 | 6% | |

| 存储器 | 0 | 0% | |

| IO管脚 | 5 | ||

| 时钟频率 | 25MHz |

知识点

- 时钟分频

- 串行/并行转换

- 数码管动态显示

参考文档

相关文档

| 文件名称 | 功能 |

|---|---|

| DLED_DISP.v | 数码管显示 |