# FPGA designs with Verilog and SystemVerilog

## Meher Krishna Patel

Created on : October, 2017 Last updated : May, 2020

# Table of contents

| Ta | able o          | of contents                                              |

|----|-----------------|----------------------------------------------------------|

| 1  | <b>Firs</b> 1.1 | Introduction                                             |

|    | 1.2             | Creating the project                                     |

|    | 1.3             | Digital design using 'block schematics'                  |

|    | 1.4             | Manual pin assignment and compilation                    |

|    | 1.5             | Load the design on FPGA                                  |

|    | 1.6             | Digital design using 'Verilog codes'                     |

|    | 1.7             | Pin assignments using '.csv' file                        |

|    | 1.8             | Converting the Verilog design to symbol                  |

|    | 1.9             | Convert Block schematic to 'Verilog code' and 'Symbol'   |

|    | 1.10            | Conclusion                                               |

|    |                 |                                                          |

| 2  | Ove             | erview 1                                                 |

|    | 2.1             | Introduction                                             |

|    | 2.2             | Modeling styles                                          |

|    |                 | 2.2.1 Continuous assignment statements                   |

|    |                 | 2.2.2 Comparators using Continuous assignment statements |

|    |                 | 2.2.3 Structural modeling                                |

|    |                 | 2.2.4 Procedural assignment statements                   |

|    |                 | 2.2.5 Mixed modeling                                     |

|    | 2.3             | Conclusion                                               |

|    | ъ.              |                                                          |

| 3  |                 | a types       2         Introduction                     |

|    | 3.1             |                                                          |

|    | 3.2             | Lexical rules                                            |

|    | 3.3             | Data types                                               |

|    | 3.4             | Logic values                                             |

|    | 3.5             | Number representation                                    |

|    | 3.6             | Signed numbers                                           |

|    | 3.7             | Operators                                                |

|    | 3.8             | Arithmetic operator                                      |

|    |                 | 3.8.1 Bitwise operators                                  |

|    |                 | 3.8.2 Relational operators                               |

|    |                 | 3.8.3 Logical operators                                  |

|    |                 | 3.8.4 Shift operators                                    |

|    |                 | 3.8.5 Concatenation and replication operators            |

|    |                 | 3.8.6 Conditional operator                               |

|    |                 | 3.8.7 Parameter and localparam                           |

|    |                 | 3.8.8 localparam                                         |

|    |                 | 3.8.9 Parameter and defparam                             |

|    | 3.9             | Conclusion                                               |

| 4        | Pro  | cedural assignments                                        | 35       |

|----------|------|------------------------------------------------------------|----------|

|          | 4.1  | Introduction                                               | 35       |

|          | 4.2  | Combinational circuit and sequential circuit               | 35       |

|          | 4.3  | Concurrent statements and sequential statements            | 36       |

|          | 4.4  | 'always' block                                             | 36       |

|          | 4.5  | Blocking and Non-blocking assignment                       | 36       |

|          | 4.6  | Guidelines for using 'always' block                        | 38       |

|          |      | 4.6.1 'always' block for 'combinational designs'           | 38       |

|          |      | 4.6.2 'always' block for 'latched designs'                 | 38       |

|          |      | 4.6.3 'always' block for 'sequential designs'              | 38       |

|          | 4.7  | If-else statement                                          | 39       |

|          | 4.8  | Case statement                                             | 40       |

|          | 4.9  | Problem with Loops                                         | 41       |

|          | 4.10 | Loop using 'if' statement                                  | 41       |

|          |      | Conclusion                                                 | 43       |

|          |      |                                                            |          |

| <b>5</b> | VH   | DL designs in Verilog                                      | 44       |

|          | 5.1  | Introduction                                               | 44       |

|          | 5.2  | VHDL designs in Verilog                                    | 44       |

|          | 5.3  | Conclusion                                                 | 45       |

|          |      |                                                            |          |

| 6        |      | ual verifications of designs                               | 46       |

|          | 6.1  | Introduction                                               | 46       |

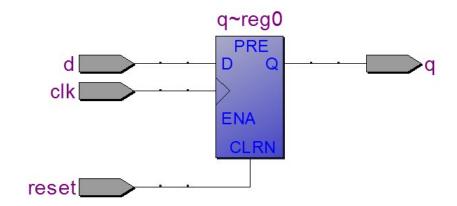

|          | 6.2  | Flip flops                                                 | 46       |

|          |      | 6.2.1 D flip flop                                          | 46       |

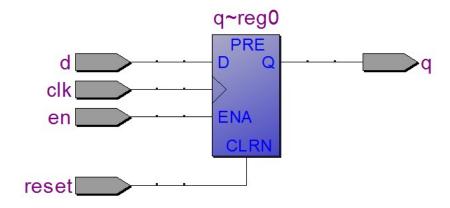

|          |      | 6.2.2 D flip flop with Enable port                         | 47       |

|          | 6.3  | Counters                                                   | 47       |

|          |      | 6.3.1 Binary counter                                       | 48       |

|          |      | 6.3.2 Mod-m counter                                        | 49       |

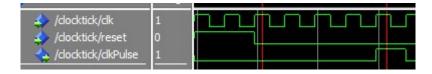

|          | 6.4  | Clock ticks                                                | 51       |

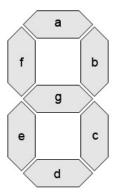

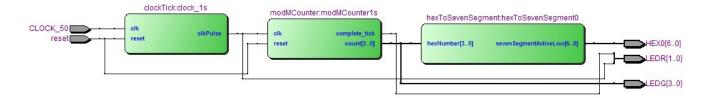

|          | 6.5  | Seven segment display                                      | 51       |

|          |      | 6.5.1 Implementation                                       | 52       |

|          |      | 6.5.2 Test design for 7 segment display                    | 53       |

|          | 6.6  | Visual verification of Mod-m counter                       | 55       |

|          | 6.7  | Conclusion                                                 | 56       |

| 7        | Fini | ite state machine                                          | 57       |

| •        |      | Introduction                                               | 57       |

|          | 7.2  | Comparison: Mealy and Moore designs                        | 57       |

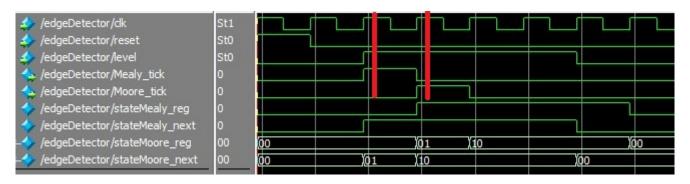

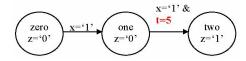

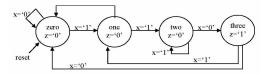

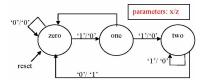

|          | 7.3  | Example: Rising edge detector                              | 57       |

|          | 1.0  | 7.3.1 State diagrams: Mealy and Moore design               | 58       |

|          |      | 7.3.2 Implementation                                       | 58       |

|          |      | 7.3.3 Outputs comparison                                   | 60       |

|          |      | 7.3.4 Visual verification                                  | 60       |

|          | 7.4  | Glitches                                                   | 61       |

|          | 1.4  | 7.4.1 Combinational design in asynchronous circuit         | 61       |

|          |      | 7.4.2 Unfixable Glitch                                     | 62       |

|          |      | 7.4.3 Combinational design in synchronous circuit          | 62       |

|          | 7 5  | $\circ$                                                    |          |

|          | 7.5  | Moore architecture and Verilog templates                   | 63       |

|          |      | 7.5.1 Regular machine                                      | 63       |

|          |      | 7.5.2 Timed machine                                        | 67       |

|          | 7.0  | 7.5.3 Recursive machine                                    | 70<br>72 |

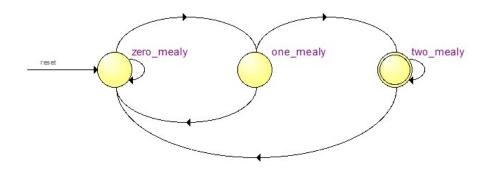

|          | 7.6  | Mealy architecture and Verilog templates                   | 73       |

|          |      | 7.6.1 Regular machine                                      | 74       |

|          |      | 7.6.2 Timed machine                                        | 75       |

|          |      | 7.6.3 Recursive machine                                    | 77       |

|          | 7.7  | Examples                                                   | 79       |

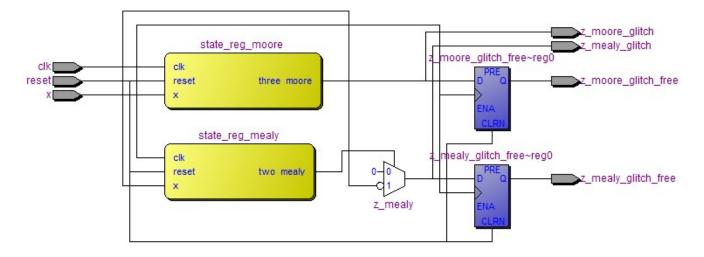

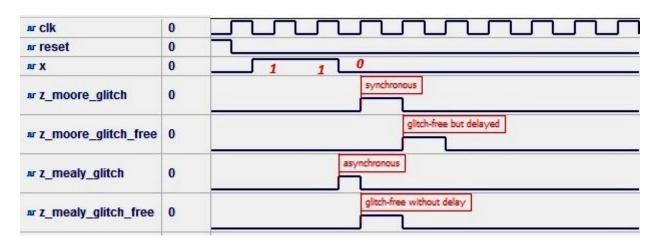

|          |      | 7.7.1 Regular Machine : Glitch-free Mealy and Moore design | 79       |

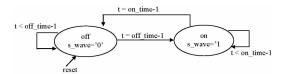

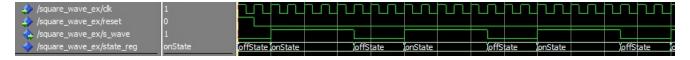

|          |      | 7.7.2 Timed machine: programmable square wave              | 84       |

|          |      |                                                            |          |

|    |      | 7.7.3 Recursive Machine: Mod-m counter      | 85           |

|----|------|---------------------------------------------|--------------|

|    | 7.8  | When to use FSM design                      | 86           |

|    | 7.9  | Conclusion                                  | 87           |

|    |      |                                             |              |

| 8  | Des  | ign Examples                                | 88           |

|    | 8.1  | Introduction                                | 88           |

|    | 8.2  | Random number generator                     | 88           |

|    |      | 8.2.1 Linear feedback shift register (LFSR) | 88           |

|    |      | 8.2.2 Visual test                           | 91           |

|    | 8.3  | Shift register                              | 91           |

|    | 0.0  | 8.3.1 Bidirectional shift register          | 92           |

|    |      |                                             |              |

|    |      | 8.3.2 Parallel to serial converter          | 94           |

|    |      | 8.3.3 Serial to parallel converter          | 95           |

|    |      | 8.3.4 Test for Parallel/Serial converters   | 96           |

|    | 8.4  | Random access memory (RAM)                  | 98           |

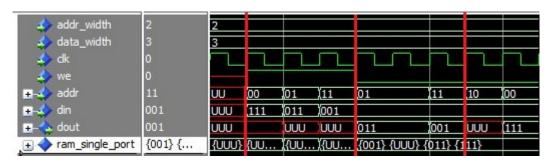

|    |      | 8.4.1 Single port RAM                       | 98           |

|    |      | 8.4.2 Visual test: single port RAM          | 100          |

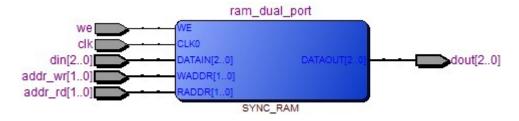

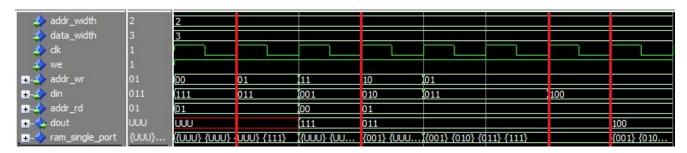

|    |      | 8.4.3 Dual port RAM                         | 101          |

|    |      |                                             | 102          |

|    | 8.5  |                                             | 103          |

|    | 0.0  |                                             | 103          |

|    |      | - ' '                                       | 103          |

|    | 9.6  |                                             | $104 \\ 105$ |

|    | 8.6  | ·                                           |              |

|    |      | <del> </del>                                | 105          |

|    |      | 8.6.2 Visual test                           | 106          |

| •  | m    |                                             | 100          |

| 9  |      |                                             | 109          |

|    | 9.1  |                                             | 109          |

|    | 9.2  |                                             | 109          |

|    |      |                                             | 109          |

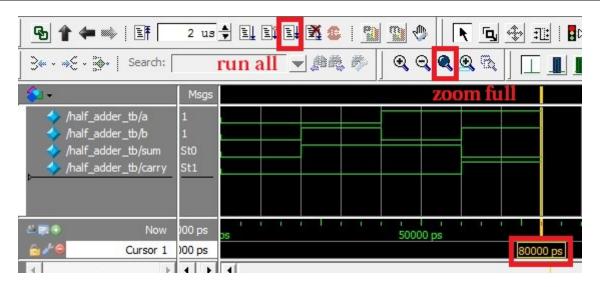

|    | 9.3  | Testbench with 'initial block'              | 110          |

|    |      | 9.3.1 Read data from file                   | 113          |

|    |      | 9.3.2 Write data to file                    | 114          |

|    | 9.4  |                                             | 115          |

|    | 9.5  |                                             | 120          |

|    | 0.0  |                                             | 0            |

| 10 | Syst | temVerilog for synthesis                    | 121          |

|    |      |                                             | 121          |

|    |      |                                             | 121          |

|    |      |                                             | 122          |

|    |      |                                             | 122 $123$    |

|    | 10.4 |                                             | _            |

|    |      | $^{\circ}$ $^{-}$                           | 123          |

|    |      |                                             | 124          |

|    |      |                                             | 125          |

|    | 10.5 |                                             | 126          |

|    |      | 10.5.1 'typedef'                            | 126          |

|    |      | 10.5.2 'enum'                               | 126          |

|    |      | 10.5.3 Example                              | 126          |

|    | 10.6 |                                             | 127          |

|    |      |                                             |              |

| 11 | Pac  | kages                                       | 128          |

| _  |      | ~                                           | 128          |

|    |      |                                             | 128          |

|    |      | 01 0                                        | $120 \\ 129$ |

|    |      | 1 1 0                                       |              |

|    | 11.4 |                                             | 130          |

|    |      | v v =1 0                                    | 130          |

|    |      | 11.4.2 Testbench                            | 130          |

| 10 | T .  |                                             | 100          |

| 12 | ınte | erface                                      | 132          |

|            | Introduction                                         |            |

|------------|------------------------------------------------------|------------|

| 12.2       | 2 Define and use interface                           | 132        |

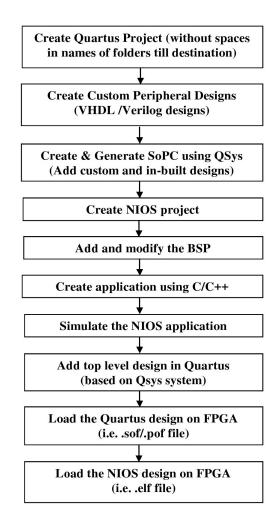

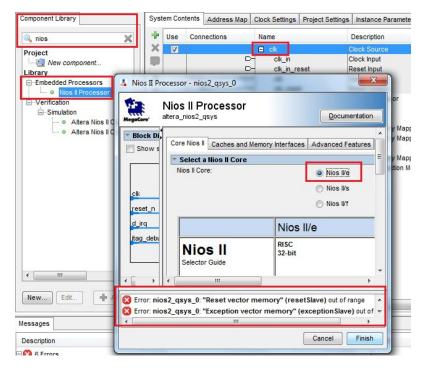

| 3 Sin      | nulate and implement SoPC design                     | 134        |

|            | Introduction                                         |            |

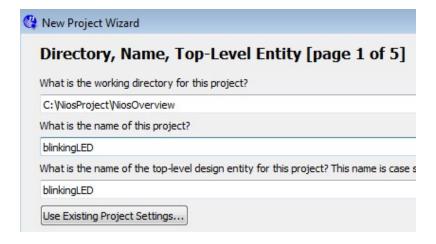

|            | 2 Creating Quartus project                           |            |

|            | 3 Create custom peripherals                          |            |

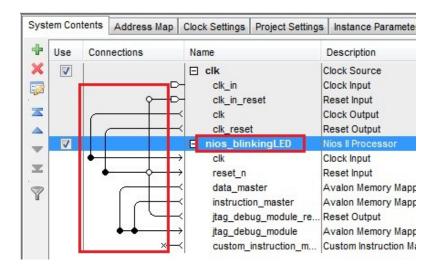

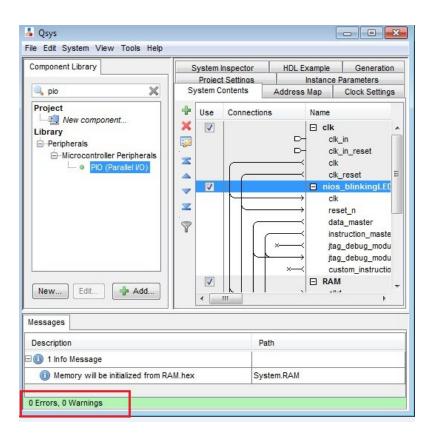

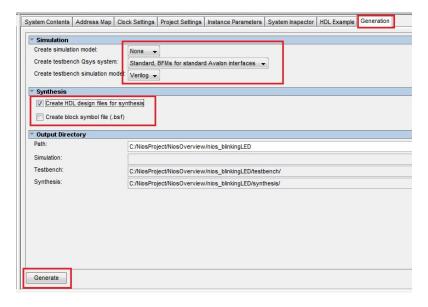

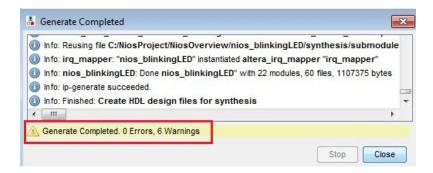

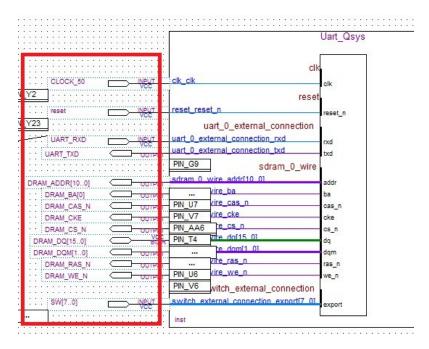

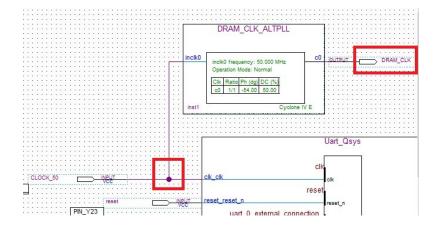

|            | 4 Create and Generate SoPC using Qsys                |            |

|            | 5 Create Nios system                                 |            |

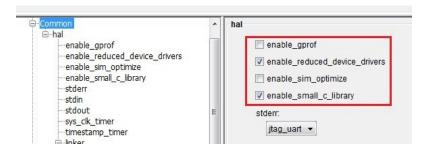

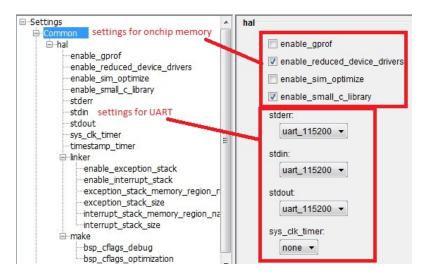

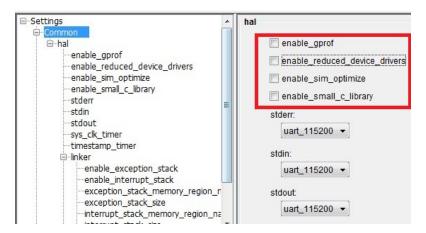

|            | 3 Add and Modify BSP                                 |            |

| 10.0       | 13.6.1 Add BSP                                       |            |

|            | 13.6.2 Modify BSP (required for using onchip memory) |            |

| 13 ′       | 7 Create application using C/C++                     |            |

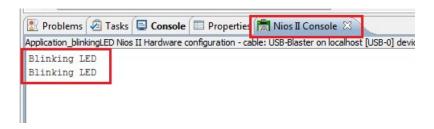

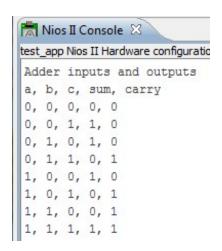

|            | B Simulate the Nios application                      |            |

|            | Adding the top level Verilog design                  |            |

|            | 10Load the Quartus design (i.esof/.pof file)         |            |

|            | 11Load the Nios design (i.e. '.elf' file)            |            |

|            | 2Saving NIOS-console's data to file                  |            |

|            | 13 Conclusion                                        |            |

| 15         | 15Conclusion                                         | 190        |

| 4 Re       | ading data from peripherals                          | 151        |

|            | Introduction                                         |            |

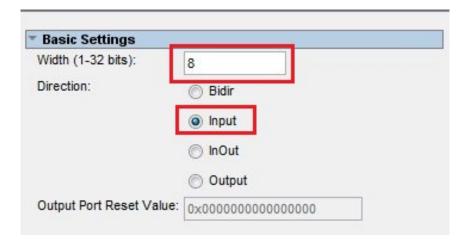

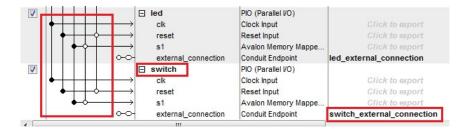

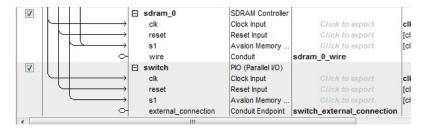

|            | 2 Modify Qsys file                                   |            |

|            | 3 Modify top level design in Quartus                 |            |

|            | 4 Modify Nios project                                |            |

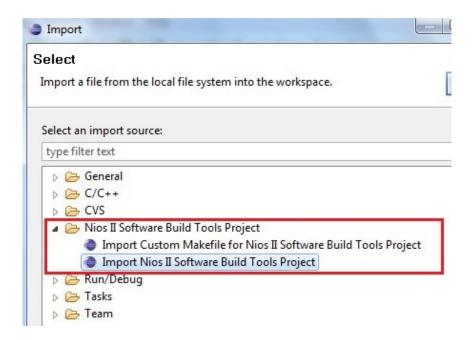

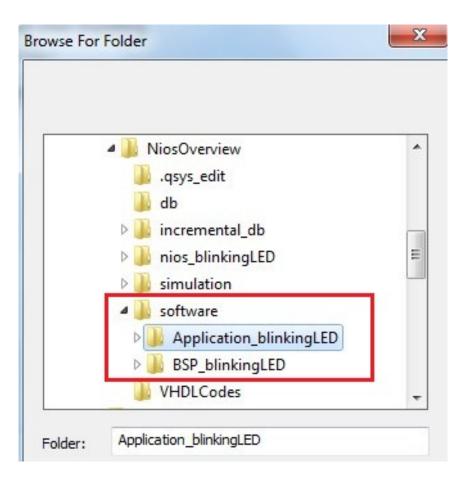

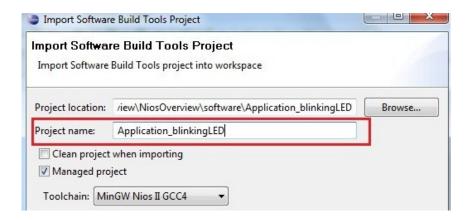

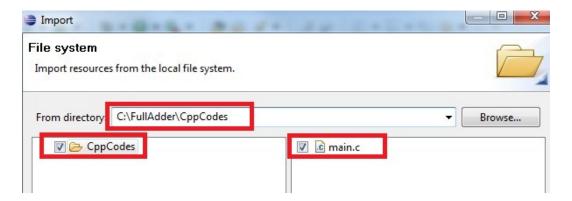

| - 1.       | 14.4.1 Adding Nios project to workspace              |            |

| 14 !       | 5 Add 'C' file for reading switches                  |            |

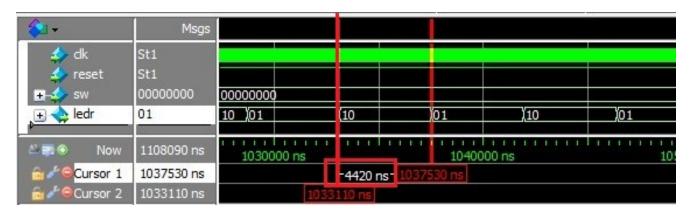

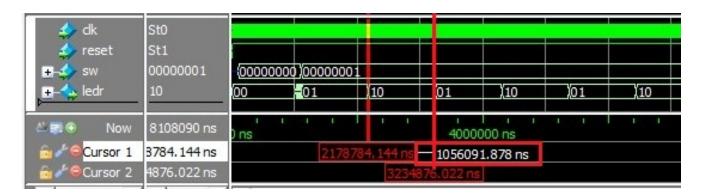

|            | Simulation and Implementation                        |            |

|            | 7 Conclusion                                         |            |

|            |                                                      | 100        |

|            |                                                      | 157        |

| 15.1       | Introduction                                         | 157        |

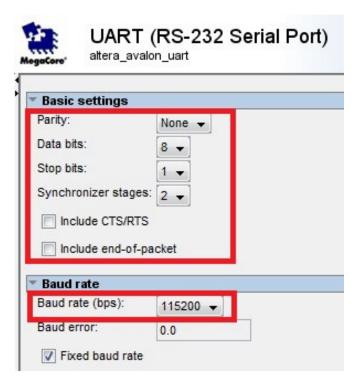

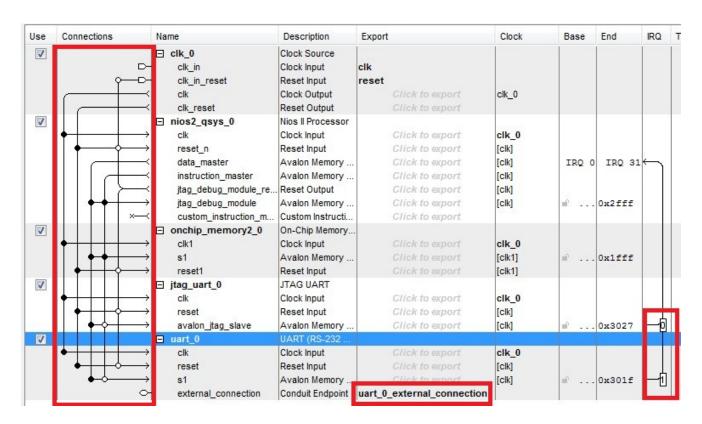

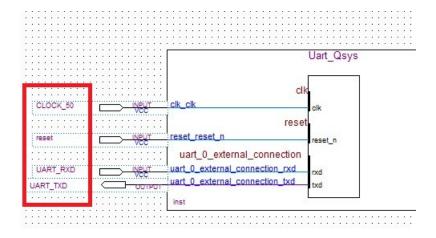

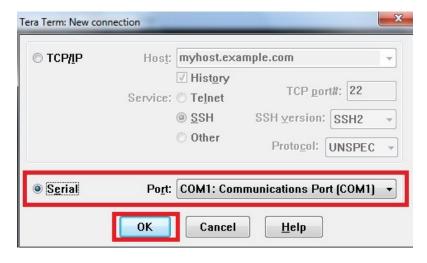

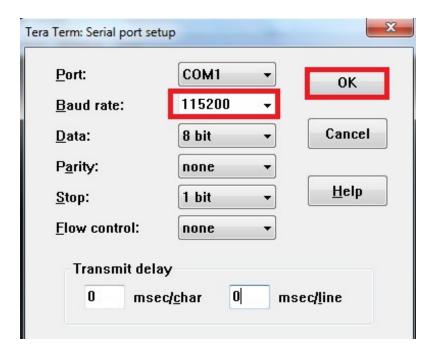

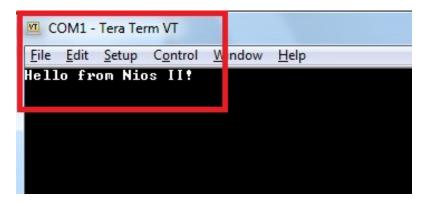

| 15.2       | 2 UART interface                                     | 157        |

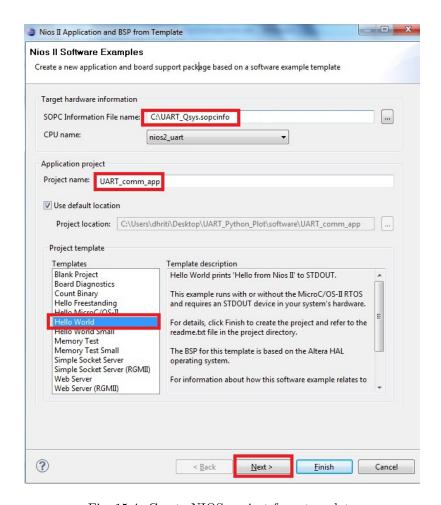

| 15.5       | 3 NIOS design                                        | 157        |

| 15.4       | 4 Communication through UART                         | 160        |

| 15.5       | 5 SDRAM Interface                                    | 162        |

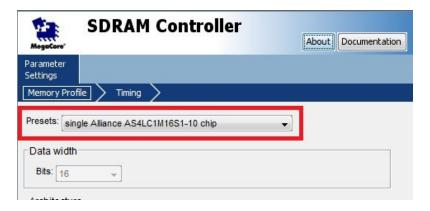

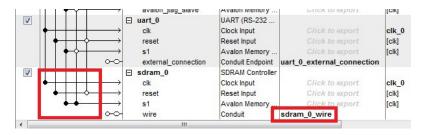

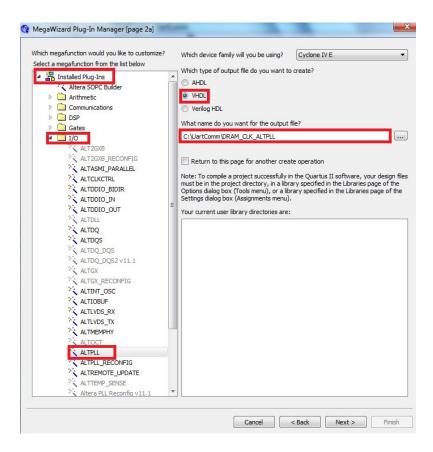

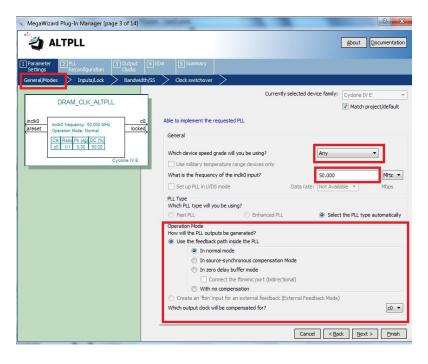

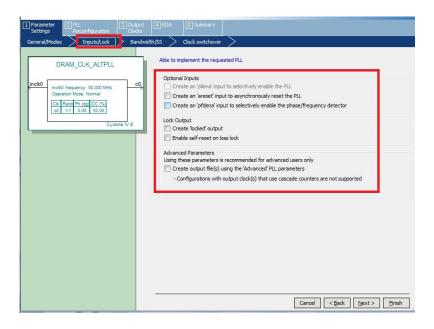

|            | 15.5.1 Modify QSys                                   | 162        |

|            | 15.5.2 Modify Top level Quartus design               | 163        |

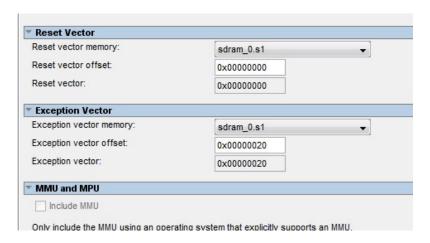

|            | 15.5.3 Updating NIOS design                          | 163        |

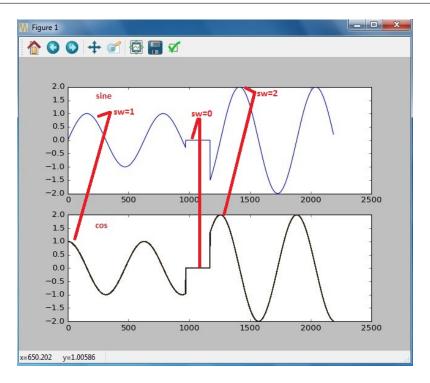

| 15.6       | 6 Live plotting the data                             | 168        |

| 15.7       | 7 Conclusion                                         | 169        |

| ~          |                                                      |            |

|            | •                                                    | 170        |

| A.1        | ·                                                    | 170        |

|            |                                                      | 170        |

|            |                                                      | 170        |

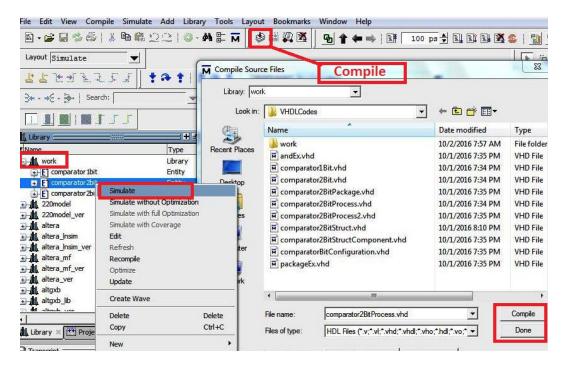

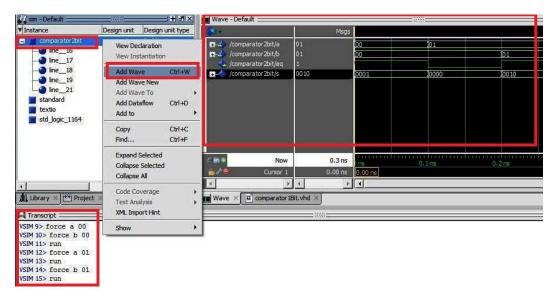

| A.2        | Modelsim                                             | 171        |

| Цa         | w to implement NIOS-designs                          | 173        |

| 110        | 1                                                    | 173        |

| -          |                                                      | 173        |

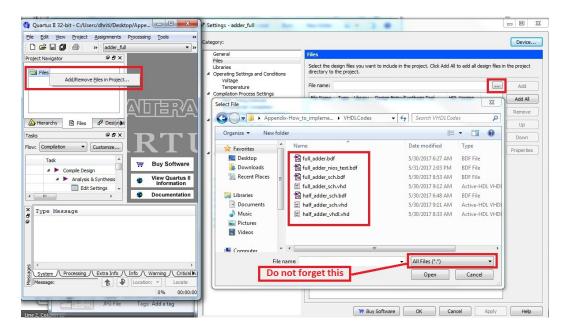

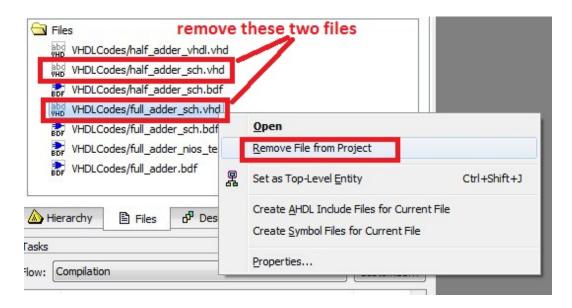

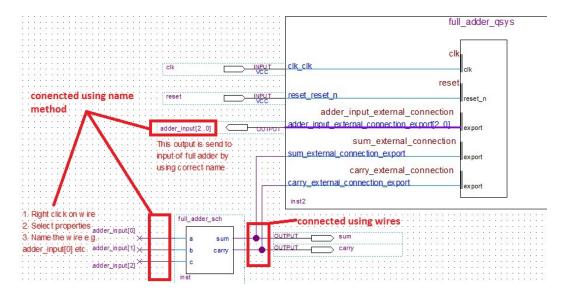

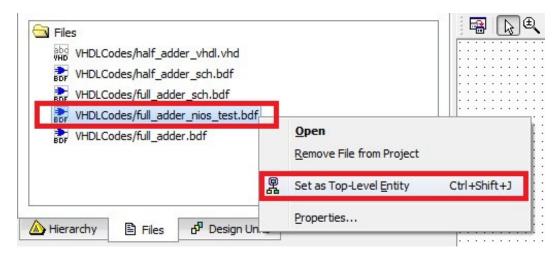

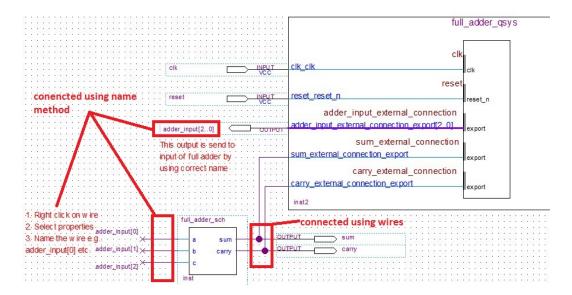

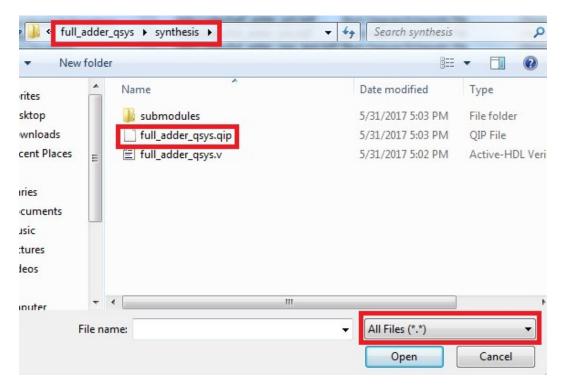

| B.1        | Add all tilgs trom Vorilog Codes tolder              | 1 ( 5      |

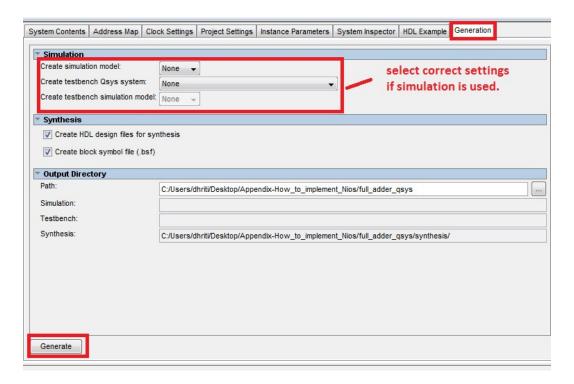

| B.1<br>B.2 |                                                      |            |

| B.1        | Generate and Add QSys system                         | 175<br>177 |

-Meher Baba

# Chapter 1

# First project

#### 1.1 Introduction

In this tutorial, full adder is designed with the help of half adders. Here we will learn following methods to create/implement the digital designs using Altera-Quartus software,

- Digital design using 'block schematics',

- Digital design using 'Verilog codes',

- Manual pin assignment for implementation,

- Pin assignments using '.csv' file,

- Loading the design on FPGA.

- Converting the 'Verilog design' to 'Symbols'

- Converting the 'Block schematic' to 'Verilog code' and 'Symbols'.

If you do not have the FPGA-board, then skip the last part i.e. 'loading the design on FPGA'. Simulation of the designs using 'Modelsim' is discussed in Chapter 2.

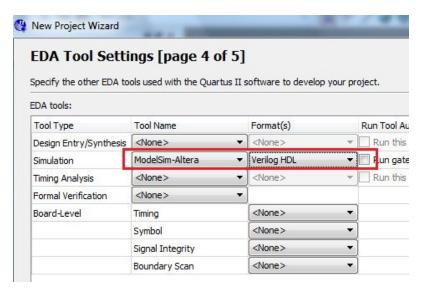

Quartus II 11.1sp2 Web Edition and ModelSim-Altera Starter software are used for this tutorial, which are freely available and can be downloaded from the Altera website. All the codes can be downloaded from the website. First line of each listing in the tutorial, is the name of the Verilog file in the downloaded zip-folder.

# 1.2 Creating the project

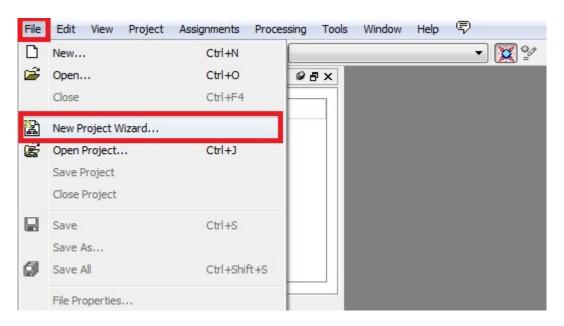

- To create a new project, first open the Quartus and go to File->New Project Wizard, as shown in Fig. 1.1.

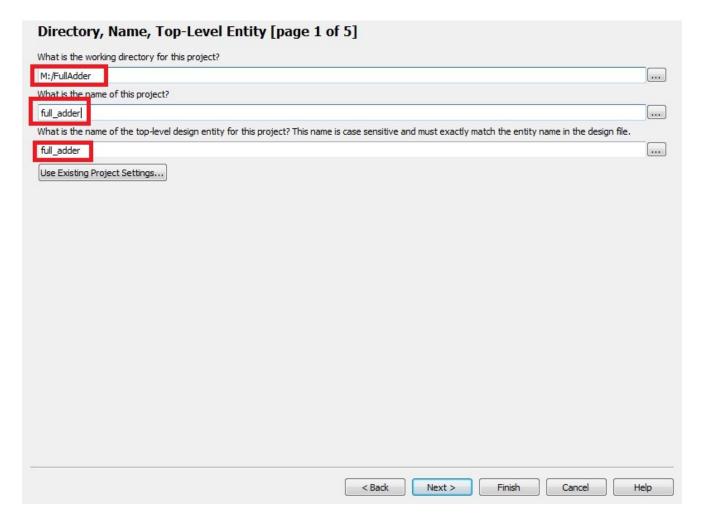

- 'Introduction' window will appear after this, click 'next' and fill the project details as shown in Fig. 1.2.

- After this, 'Add files' window will appear, click on 'next' here as we do not have any file to add to this project.

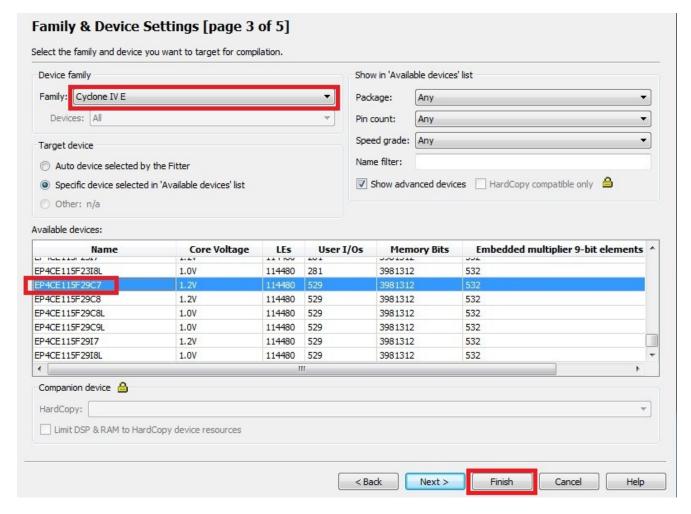

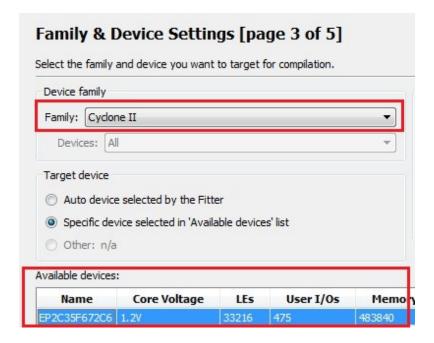

- Next, 'Family and Device settings' page will appear, select the proper device setting based on your FPGA board and click 'Finish' as shown in Fig. 1.3. If you don't have FPGA board, then simply click 'Finish'.

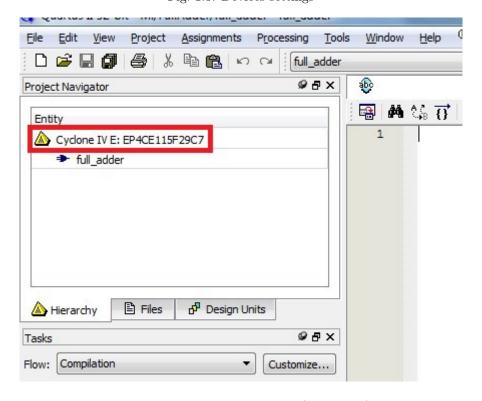

- After clicking on finish, the project will be created as shown in Fig. 1.4. Note that, the tutorials are tested on DE2-115, DE2 (cyclone-II family) or DE0-Nano boards, therefore project settings may be different for different chapters. You need to select the correct device while running the code on your system. This can be done by double-clicking on the device name, as shown in Fig. 1.4.

# 1.3 Digital design using 'block schematics'

Digitals design can be create using two methods i.e. using 'block-schematics' and with 'programming language e.g. VHDL or Verilog' etc. Both have their own advantages in the design-process, as we will observe in the later

Fig. 1.1: Create new project

Fig. 1.2: Name and location of project

Fig. 1.3: Devices settings

Fig. 1.4: Update device settings (if required)

chapters of the tutorial.

In this section, we will create a half adder using block-schematics method, as shown below,

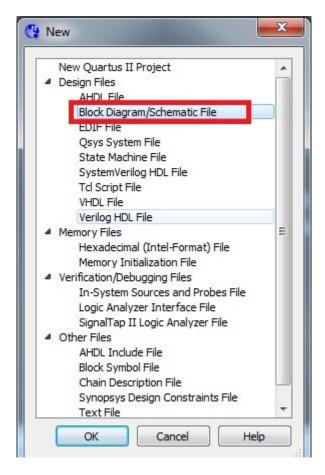

• For this, click on File—>New—>Block diagram/Schematics files, as shown in Fig. 1.5; and a blank file will be created.

Fig. 1.5: Create new block schematics

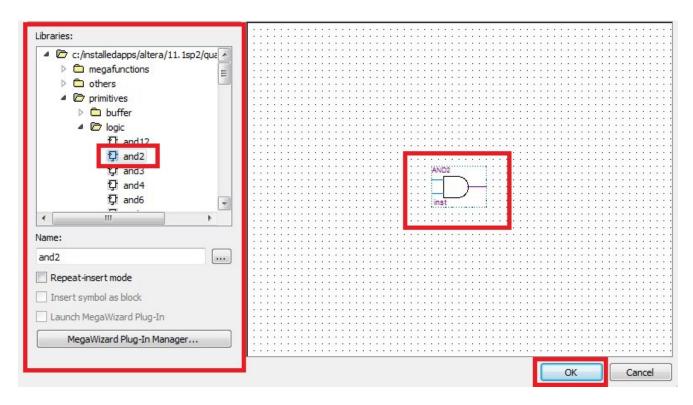

- Double click (anywhere) in the blank file, and a window will pop-up; select the 'and' gate from this window as shown in Fig. 1.6. Similarly, select the 'xor' gate.

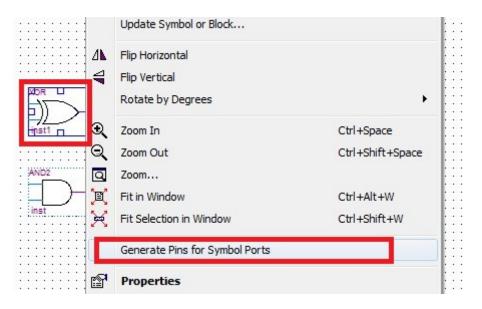

- Next, right click on the 'xor' gate and then click on 'Generate Pins for Symbol Ports', as shown in Fig. 1.7.

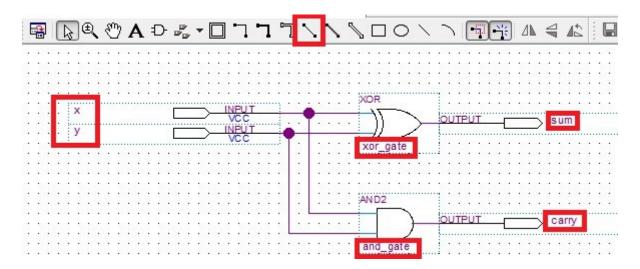

- Now, connect the input ports of 'xor' gate with 'and' gate (using mouse); then Next, right click on the 'and' gate and then click on 'Generate Pins for Symbol Ports'. Finally rename the input and output ports (i.e. x, y, sum and carry) as shown in Fig. 1.8.

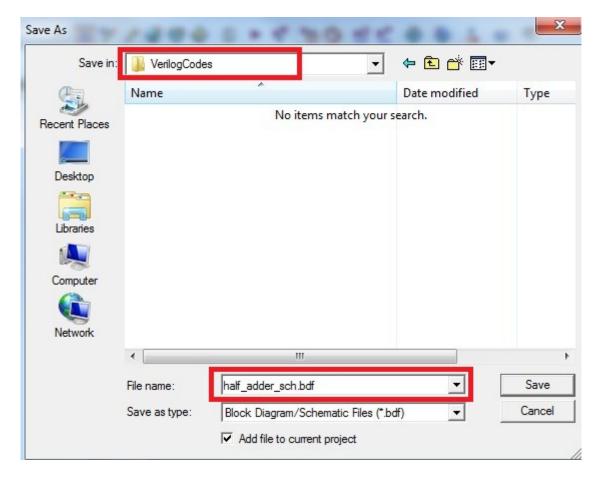

- Finally, save the design with name 'half\_adder\_sch.bdf'. It's better to save the design in the separate folder, so that we can distinguish the user-defined and system-generated files, as shown in Fig. 1.9 where Verilog codes are saved inside the 'VerilogCodes' folders, which is inside the main project directory.

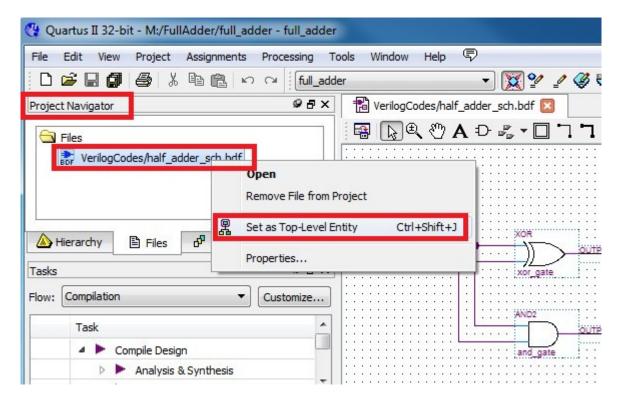

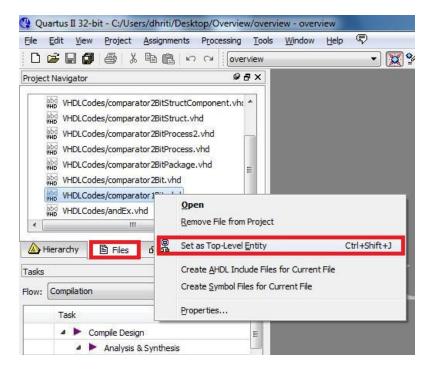

- Since the project name is 'full\_adder', whereas the half adder's design name is 'half\_adder\_sch.bdf' (i.e. not same as the project name), therefore we need to set this design as top level entity for compiling the project. For this, go to project navigator and right click on the 'half\_adder\_sch.bdf' and set it as top level entity, as shown in Fig. 1.10.

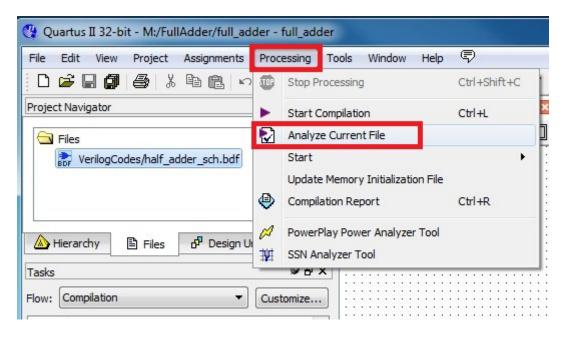

- Now, we can analyze the file as shown in Fig. 1.11. If all the connections are correct that analysis option will not show any error.

Note that, 'start compilation' option (above the Analyse option in the figure) is used when we want to generate the .sof/.pof file, to load the design on the FPGA, whereas analyze option is used to generate the RTL view only. We will use 'compilation' option in next section.

Fig. 1.6: Select 'and' gate

Fig. 1.7: Add ports

Fig. 1.8: Make connections

Fig. 1.9: Save project in separate directory i.e. VerilogCodes here

Fig. 1.10: Select top level entity for the project

Fig. 1.11: Analyze the design

## 1.4 Manual pin assignment and compilation

Please enter correct pin location according to your FPGA board, as shown in this section. If you do not have the board, then skip this section and go to Section 1.6.

Once design is analyzed, then next step is to assign the correct pin location to input and output ports. This can be done manually or using .csv file. In this section, we will assign pin manually. Follow the below steps for pin assignments,

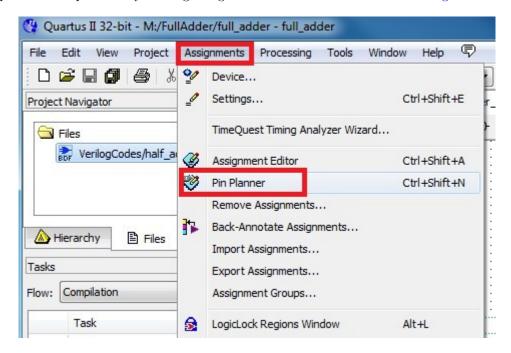

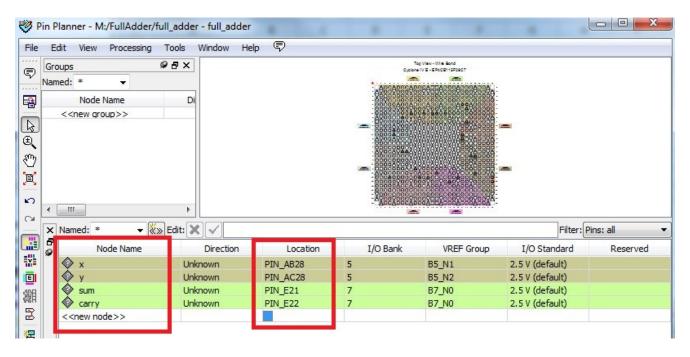

• First open the 'Pin-planner' by clicking Assignments—>Pin Planner as shown in Fig. 1.12.

Fig. 1.12: Pin planner

- Next, type the names of the input and output ports along with the pin-locations on the board, as shown in Fig. 1.13. Details of the Pin-locations are provided with the manual of the FPGA-boards e.g. in DE2-115 board, pin 'PIN\_AB28' is connected with switch SW0. By assign this pin to 'x', we are connecting the port 'x' with switch SW0.

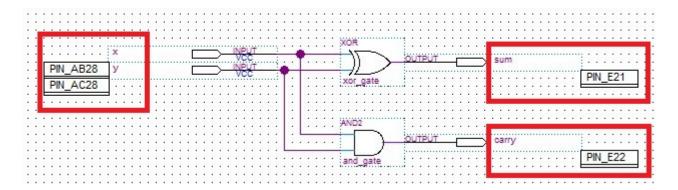

- After assigning the pin, analyze the design again (see Fig. 1.11). After this, we can see the pin numbers in the '.bdf' file, as shown in Fig. 1.14.

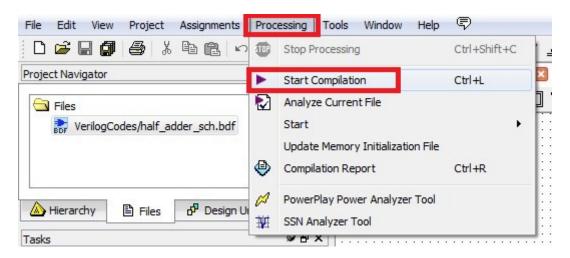

- Finally, compile the design using 'ctrl+L' button (or by clicking processing->Start compilation, as shown in Fig. 1.15).

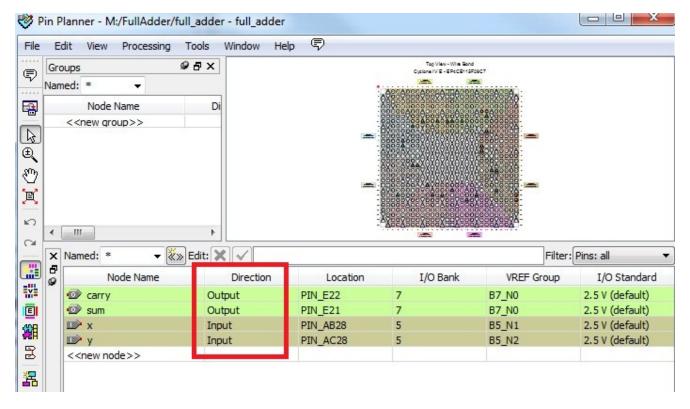

- After successful compilation, if we see the pin-assignment again, then we will find that direction of the pin are assigned now, as shown in Fig. 1.16 (which were set to 'unknown' during analysis as in Fig. 1.13)

# 1.5 Load the design on FPGA

Follow the below, steps to load the design on FPGA,

- Connect the FPGA to computer and turn it on.

- Full compilation process generates the .sof/.pof files, which can be loaded on the FPGA board. To load the design on FPGA board, go to Tools->Programmer. And a programmer window will pop up.

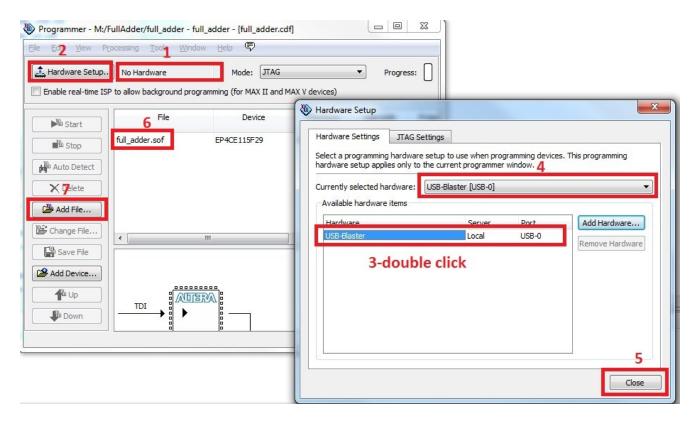

- In the programmer window (see Fig. 1.17), look for two things i.e. position '1' should display 'USB-BLASTER' and position '6' should display the '.sof' file. If any of this mission then follow below steps,

Fig. 1.13: Pin assignment

Fig. 1.14: Assigned pins to ports

Fig. 1.15: Start compilation

Fig. 1.16: Direction of the ports

- If USB-BLASTER is missing, then click on 'Hardware setup (location 2 in Fig. 1.17)' and then double click on USB-BLASTER in the pop-up window (location 3). This will display the USB-BLASTER at location 4. Finally close the pop-up window.

- If '.sof' file is not displayed at location 6, then click on 'Add file...' (location 7) and select the '.sof' file from main project directory (or in output files folder in main project directory).

- Finally click on the 'start' button in Fig. 1.17 and check the operation of 'half adder' using switches SW0 and SW1; output will be displayed on green LEDs i.e. LEDG0 and LEDG1.

# 1.6 Digital design using 'Verilog codes'

In this section, half adder is implemented using Verilog codes. For this, click on File->New->Verilog files, as shown in Fig. 1.5; and a blank file will be created. Type the Listing Listing 1.1 in this file and save it as 'half adder verilog.v'.

Now, set this design as 'top level entity' (Fig. 1.10). We can analyze the design now, but we will do it after assigning the pins using .csv file in next section.

Listing 1.1: Verilog code for half adder

```

module half_adder_verilog(

input wire a, b,

output wire sum, carry

);

assign sum = a ^ b;

assign carry = a & b;

endmodule

```

Fig. 1.17: Load the design on FPGA

## 1.7 Pin assignments using '.csv' file

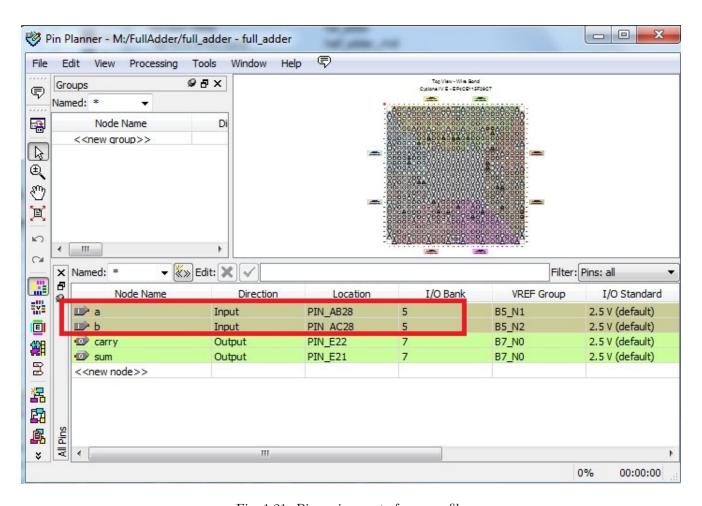

In this section, we will learn to assign the pins using .csv files. Note that, we used input port as 'a' and 'b' in Verilog design (instead of 'x' and 'y' as in Fig. 1.8), so that we can observe the changes in the pin assignments.

To assign the pins using csv file, follow the below steps,

• First type the content in Fig. 1.18 in a text-file and save it as 'pin assg file.csv'.

```

To,Location

a,PIN_AB28

b,PIN_AC28

sum,PIN_E21

carry,PIN_E22

```

Fig. 1.18: Content of pin assg file.csv

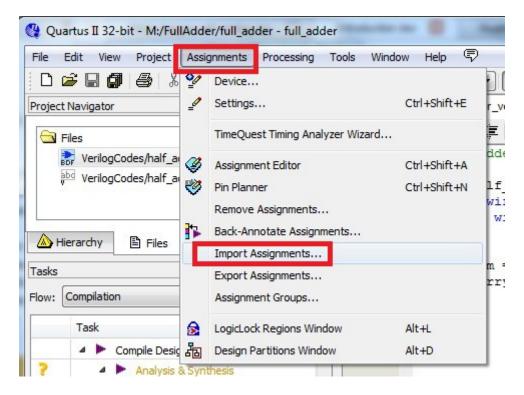

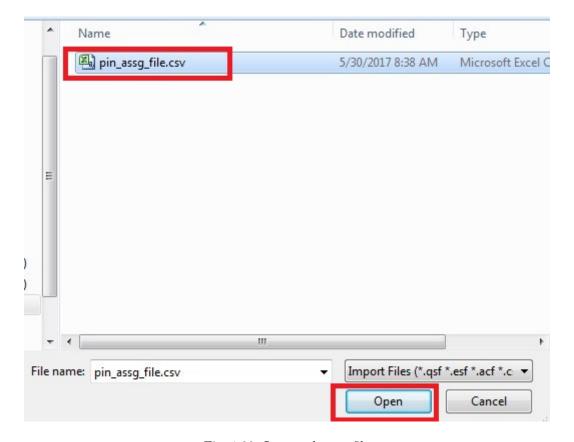

- Next, click on the Assignments—>Import Assignments as shown in Fig. 1.19. And locate the file pin\_assg\_file.csv by clicking on the cdots button, in the popped-up window, as shown in Fig. 1.20.

- Now, analyze the design (Fig. 1.11) and then open the pin planner (Fig. 1.12). We can see the new pin assignments as shown in Fig. 1.21 (If proper assignments do not happen, then check whether the Verilog design is set as top level or not and import assignments again and analyze the design).

- Finally, compile and load and check the design as discussed in Section 1.5.

# 1.8 Converting the Verilog design to symbol

Verilog code can be converted into block schematic format, which is quite useful for connecting various modules together. In this section, half adder's Verilog file is converted into schematic and then two half adder is connected

Fig. 1.19: Import assignments

Fig. 1.20: Locate the csv file  $\frac{1}{2}$

Fig. 1.21: Pin assignments from  $\operatorname{csv}$  file

to make a full adder. Note that, this connection can be made using Verilog code as well, which is discussed in Chapter 2.

Follow the below steps to create a full adder using this method,

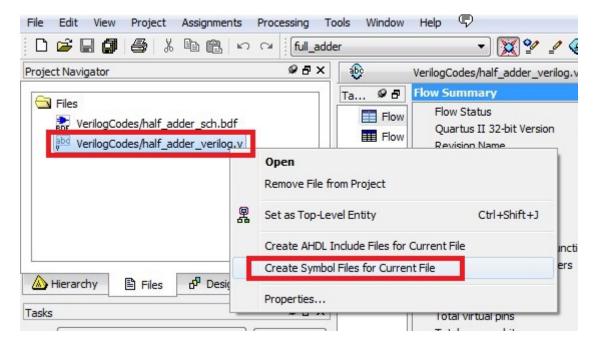

• Right click on the 'half\_adder\_verilog.v' and click on 'Create symbol file for current file' as shown in Fig. 1.22. It will create a symbol for half adder design.

Fig. 1.22: Convert Verilog code to symbol

- Now, create a new 'block schematic file' (Fig. 1.5).

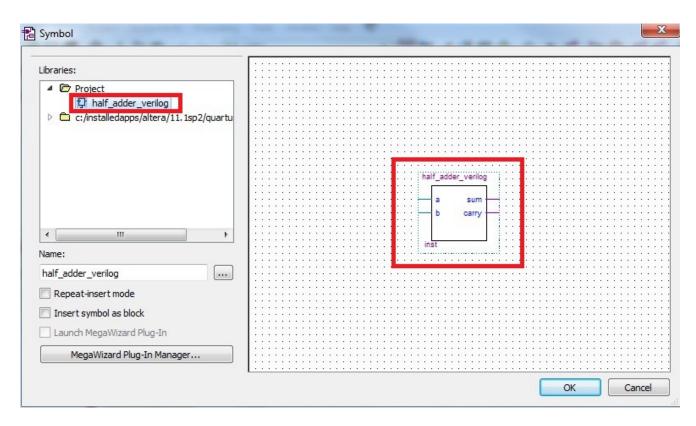

- Next, double click on this file and add the half adder symbol as shown in Fig. 1.23.

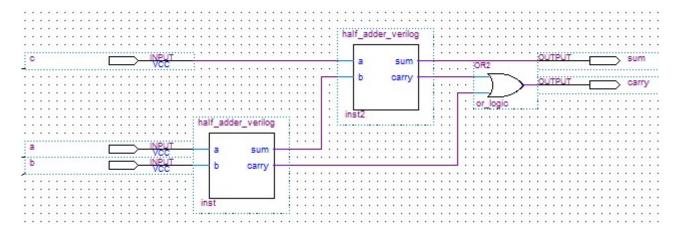

- Again add one more 'half adder symbol' along with 'or' gate and connect these components as shown in Fig. 1.24.

- Since, one more port (i.e. c) is added to the design, therefore modify the 'pin\_assg\_file.csv' as shown in Fig. 1.25.

- Save the design as 'full\_adder\_sch.bdf'.

- Import the assignment again; and compile the design (see pin assignments as well for 5 ports i.e. a, b, c, sum and carry). Finally load the design on FGPA.

# 1.9 Convert Block schematic to 'Verilog code' and 'Symbol'

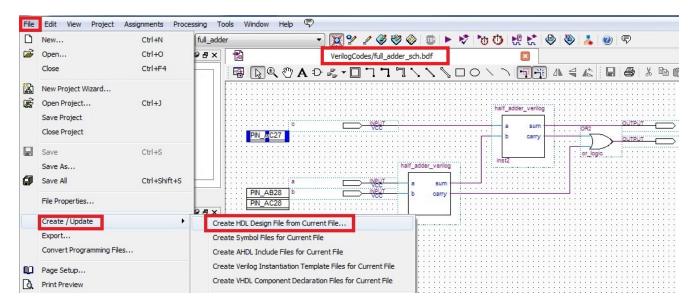

We can convert the '.bdf' file to Verilog code as well. In this section, full adder design is converted to Verilog code. For this open the file 'full\_adder\_sch.bdf'. Then go to File->Create/Update->Create HDL Design File... as shown in Fig. 1.26 and select the file type as 'Verilog' and press OK; the file will be saved in the VerilogCodes folder (see Fig. 1.27). The content of the generated 'Verilog' file are shown in Listing 1.2.

Now, we can convert this Verilog code into symbol as shown in Section 1.8.

**Note:** Note that, if we want to convert the '.bdf' file into symbol, then we need to convert it into Verilog code first, and then we can convert the Verilog code into symbol file.

Fig. 1.23: Add half adder symbol

Fig. 1.24: Full adder using half adders

To,Location

a,PIN\_AB28

b,PIN\_AC28

c,PIN\_AC27

sum,PIN\_E21

carry,PIN\_E22

Fig. 1.25: Update pin assignments

Fig. 1.26: Convert schematic to Verilog

Fig. 1.27: Select Verilog

Listing 1.2: Verilog code for full adder

```

module full_adder_sch(

2

3

b,

С,

sum,

5

carry

6

);

input wire

10

input wire

b;

input wire

с;

output wire sum;

12

output wire carry;

13

14

SYNTHESIZED_WIRE_0;

wire

15

SYNTHESIZED_WIRE_1;

wire

16

SYNTHESIZED_WIRE_2;

17

18

19

half_adder_verilog b2v_inst(

20

.a(a),

21

.b(b),

22

.sum(SYNTHESIZED_WIRE_0),

23

.carry(SYNTHESIZED_WIRE_1));

24

25

26

half_adder_verilog b2v_inst2(

27

.a(c),

28

.b(SYNTHESIZED_WIRE_0),

29

.sum(sum),

30

.carry(SYNTHESIZED_WIRE_2));

31

32

assign carry = SYNTHESIZED_WIRE_1 | SYNTHESIZED_WIRE_2;

33

34

35

endmodule

36

```

#### 1.10 Conclusion

In this chapter, we learn to implement the design using schematic and coding methods. Also, we did the pin assignments manually as well as using csv file. Finally, we learn to convert the Verilog code into symbol file; and schematic design into Verilog code.

**Note:** Please see the Appendix B as well, where some more details about symbol connections are shown, along with the methods for using the codes provided in this tutorial.

1.10. Conclusion

Anything beyond your capacity will necessarily change your capacity, because so long as everything is within your limits, you don't know what is beyond them.

-Meher Baba

# Chapter 2

# Overview

#### 2.1 Introduction

Verilog is the hardware description language which is used to model the digital systems. In this tutorial, following 4 elements of Verilog designs are discussed briefly, which are used for modeling the digital system.

- Design with Continuous assignment statements

- Structural design

- Design with Procedural assignment statements

- Mixed design

The 2-bit comparators are implemented using various methods and corresponding designs are illustrated, to show the differences in these methods. Note that, all the features of Verilog can not be synthesized i.e. these features can not be converted into designs. Only, those features of Verilog are discussed in this tutorial, which can be synthesized.

## 2.2 Modeling styles

In Verilog, the model can be designed in four ways as shown in this section. Two bit comparator is designed with different styles; which generates the output '1' if the numbers are equal, otherwise output is set to '0'.

#### 2.2.1 Continuous assignment statements

In this modeling style, the relation between input and outputs are defined using signal assignments. 'assign' keyword is used for this purpose. In the other words, we do not define the structure of the design explicitly; we only define the relationships between the signals; and structure is implicitly created during synthesis process.

#### **Explanation Listing 2.1:**

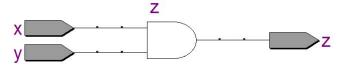

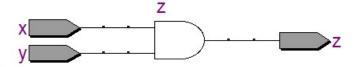

Listing 2.1 is the example of 'Continuous assignment statements' design, where relationship between inputs and output are given in line 8. In verilog, '&' sign is used for 'and' operation (line 8), and '//' is used for comments (line 1). The 'and gate (i.e. RTL view)' generated by Listing 2.1 is shown in Fig. 2.1.

Note: To see the RTL view of the design, go to Tools->Netlist Viewers->RTL viewer

Note that, in lines 4 and 5, 'wire' keyword is used which is the 'data type'. For continuous assignment statements 'wire' keyword is used; whereas 'reg' keyword is used for procedural assignment statement. Further, input ports can not be defined as 'reg'. Note that, these keyword are not interchangeable and

the differences between these 'data types' are discussed in Section 2.2.4. Further, more operators e.g. 'and', 'not' and 'nand' etc. are discussed in Chapter 3.

#### Listing 2.1: And gate

```

1  // andEx.v

2

3  module andEx(

4   input wire x, y,

5   output wire z

6 );

7

8  assign z = x & y; // x and y

9  endmodule

```

Fig. 2.1: And gate, Listing 2.1

• Listing 2.1 can be written as Listing 2.2, where module-definition contains name of ports only (Line 3); and types of ports are defined outside the module (Lines 5-6).

Listing 2.2: And gate

```

module andEx2(x, y, z);

module andEx2(x, y, z);

input wire x, y;

output wire z;

assign z = x & y;

endmodule

```

#### 2.2.2 Comparators using Continuous assignment statements

In this section, two more examples of Continuous assignment statements are shown i.e. '1 bit' and '2 bit' comparators; which are used to demonstrate the differences between various modeling styles in the tutorial. Fig. 2.2 and Fig. 2.3 show the truth tables of '1 bit' and '2 bit' comparators. As the name suggests, the comparator compare the two values and sets the output 'eq' to 1, when both the input values are equal; otherwise 'eq' is set to zero. The corresponding boolean expressions are shown below,

For 1 bit comparator:

$$eq = x'y' + xy \tag{2.1}$$

For 2 bit comparator:

$$eq = a'[1]a'[0]b'[1]b'[0] + a'[1]a[0]b'[1]b[0] + a[1]a'[0]b[1]b'[0] + a[1]a[0]b[1]b[0]$$

(2.2)

Above two expressions are implemented using verilog in Listing 2.3 and Listing 2.4, which are explained below.

Explanation Listing 2.3:

| x | У | eq |

|---|---|----|

| 0 | 0 | 1  |

| 0 | 1 | 0  |

| 1 | 0 | 0  |

| 1 | 1 | 1  |

Fig. 2.2: 1 bit comparator, Listing 2.3

| a[1] a[0] | b[1] b[0] | eq |

|-----------|-----------|----|

| 0 0       | 0 0       | 1  |

| 0 0       | 0 1       | 0  |

| 0 0       | 10        | 0  |

| 0 0       | 11        | 0  |

| 0 1       | 00        | 0  |

| 0 1       | 01        | 1  |

| 0 1       | 10        | 0  |

| 0 1       | 11        | 0  |

| 10        | 0 0       | 0  |

| 10        | 01        | 0  |

| 10        | 10        | 1  |

| 10        | 11        | 0  |

| 11        | 0 0       | 0  |

| 11        | 01        | 0  |

| 11        | 10        | 0  |

| 11        | 11        | 1  |

Fig. 2.3: 2 bit comparator, Listing 2.4

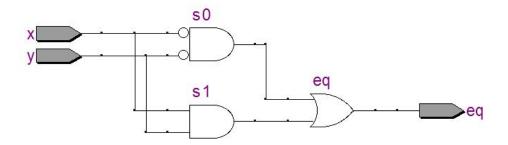

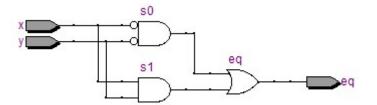

Listing 2.3 implements the 1 bit comparator based on (2.1). Two intermediate signals are defined in Line 8. These two signals (s0 and s1) are defined to store the values of x'y' and xy respectively. Values to these signals are assigned at Lines 10 and 11. In verilog, 'not' and 'or' operations are implemented using '~' and '|' signs as shown in Line 10 and 12 respectively. Finally (2.1) performs 'or' operation on these two signals, which is done at Line 12. When we compile this code using 'Quartus software', it implements the code into hardware design as shown in Fig. 2.4.

The compilation process to generate the design is shown in Appendix B. Also, we can check the inputoutput relationships of this design using Modelsim, which is also discussed briefly in Appendix B.

Listing 2.3: Comparator 1 Bit

```

comparator 1Bit.v

1

2

module comparator1Bit(

3

input wire x, y,

output wire eq

5

);

6

7

8

wire s0, s1;

9

assign s0 = ~x & ~y;

10

assign s1 = x & y;

11

12

assign eq = s0 \mid s1;

13

endmodule

```

**Note:** Note that, the statements in 'Continuous assignment statements' and 'structural modeling' (described in Section 2.2.3) are the concurrent statements, i.e. these statements execute in parallel. In the other words, order of statements do not affect the behavior of the circuit; e.g. if we exchange the Lines 10, 11 and 12 in Listing 2.3, again we will get the Fig. 2.4 as implementation.

On the other hand, statements in 'Procedural assignment statements' (described in Section 2.2.4) executes sequentially and any changes in the order of statements will change the behavior of circuit.

#### Explanation :numref: Fig. 2.4

Fig. 2.4 is generated by Quartus software according to the verilog code shown in Listing 2.3. Here, so is the 'and' gate with inverted inputs x and y, which are generated according to Line 10 in Listing 2.3. Similarly, s1 'and' gate is generated according to Line 11. Finally output of these two gates are applied to 'or' gate (named as 'eq') which is defined at Line 12 of the Listing 2.3.

Fig. 2.4: 1 bit comparator, Listing 2.3

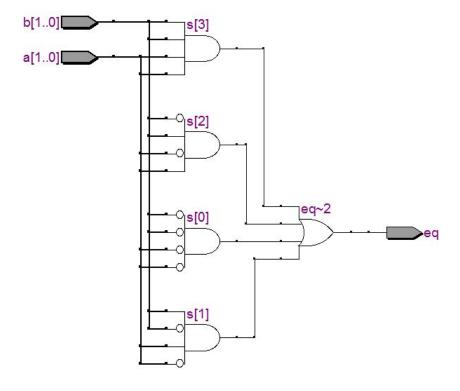

#### **Explanation Listing 2.4**

This listing implements the equation (2.2). Here, we are using two bit input, therefore 'wire[1:0]' is used at line 4. '1:0' sets the 1 as MSB (most significant bit) and 0 as LSB(least significant bit) i.e. the a[1] and b[1] are the MSB, whereas a[0] and b[0] are the LSB. Since we need to store four signals (lines

10-13), therefore 's' is defined as 4-bit vector in line 8. Rest of the working is same as Listing 2.3. The implementation of this listing is shown in Fig. 2.5.

Listing 2.4: Comparator 2 Bit

```

// comparator2Bit.v

2

module comparator2Bit(

3

input wire[1:0] a, b,

4

output wire eq

5

);

6

wire[3:0] s;

8

9

assign s[0] = a[1] & a[0] & b[1] & b[0];

10

assign s[1] = a[1] & a[0] & b[1] & b[0];

11

assign s[2] = a[1] \& ~a[0] \& b[1] \& ~b[0];

12

assign s[3] = a[1] & a[0] & b[1] & b[0];

13

14

assign eq = s[0] | s[1] | s[2] | s[3];

15

endmodule

16

```

Fig. 2.5: 2 bit comparator, Listing 2.4

#### 2.2.3 Structural modeling

In previous section, we designed the 2 bit comparator based on equation (2.2) . Further, we can design the 2 bit comparator using 1-bit comparator as well, with following steps,

- First compare each bit of 2-bit numbers using 1-bit comparator; i.e. compare a[0] with b[0] and a[1] with b[1] using 1-bit comparator (as shown in Fig. 2.3).

- If both the values are equal, then set the output 'eq' as 1, otherwise set it to zero.

This method is known as 'structural' modeling, where we use the pre-defined designs to create the new designs (instead of implementing the 'boolean' expression). This method is quite useful, because most of the large-systems

are made up of various small design units. Also, it is easy to create, simulate and check the various small units instead of one large-system. Listing 2.5 is the example of structural designs, where 1-bit comparator is used to created a 2-bit comparator.

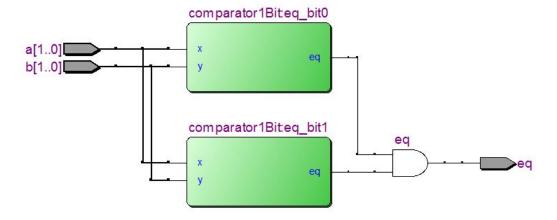

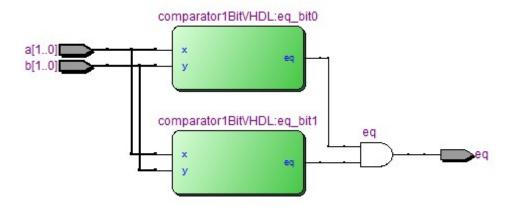

#### **Explanation Listing 2.5**

In this listing, Lines 4-5 define the two input ports of 2-bit size and one 1-bit output port. Then two signals are defined (Line 8) to store the outputs of two 1-bit comparators, as discussed below.

'eq\_bit0' and 'eq\_bit1' in Lines 10 and 11 are the names of the two 1-bit comparator, which are used in this design. We can see these names in the resulted design, which is shown in Listing 2.5.

Next, 'comparator1Bit' in Lines 10 and 11 is the name of the 1-bit comparator (defined in Listing 2.3). With this declaration, i.e. comparator1bit, we are calling the design of 1-bit comparator to current design.

Then, mapping statements e.g. x(a[0]) in Lines 10 and 11, are assigning the values to the input and output port of 1-bit comparator. For example, in Line 10, input ports of 1-bit comparator i.e. x and y, are assigned the values of a[0] and b[0] respectively from this design; and the output y of 1-bit comparator is stored in the signal s0. Further, in Line 13, if signals s0 and s1 are 1 then 'eq' is set to 1 using 'and' gate, otherwise it will be set to 0. Final design generated by Quartus software for Listing 2.5 is shown in Fig. 2.6.

Listing 2.5: Structure modeling using work directory

```

// comparator2BitStruct.v

1

2

module comparator2BitStruct(

3

input wire[1:0] a, b,

4

5

output wire eq

);

6

7

wire s0, s1;

8

9

comparator1Bit eq_bit0 (.x(a[0]), .y(b[0]), .eq(s0));

10

11

comparator1Bit eq_bit1 (.x(a[1]), .y(b[1]), .eq(s1));

12

13

assign eq = s0 & s1;

endmodule

```

Fig. 2.6: 2 bit comparator, Listing 2.5

#### Explanation Fig. 2.6

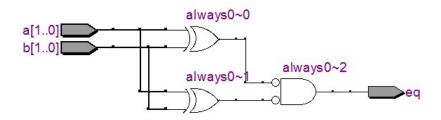

In this figure, a[1..0] and b[1..0] are the input bits whereas 'eq' is the output bit. Thick Lines after a[1..0] and b[1..0] show that there are more than 1 bits e.g. in this case these Lines have two bits. These thick Lines are changed to thin Lines before going to comparators; which indicates that only 1 bit is sent as input to comparator.

In 'comparator1Bit: eq\_bit0', 'comparator1Bit' is the name of the module defined for 1-bit comparator (Listing 2.3); whereas the 'eq\_bit0' is the name of this module defined in Line 10 of listing Listing 2.5. Lastly outputs of two 1-bit comparator are sent to 'and' gate according to Line 13 in listing Listing 2.5.

Hence, from this figure we can see that the 2-bit comparator can be designed by using two 1-bit comparator.

#### 2.2.4 Procedural assignment statements

In Procedural assignment statements, the 'always' keyword is used and all the statements inside the always statement execute sequentially. Various conditional and loop statements can be used inside the process block as shown in Listing 2.6. Further, always blocks are concurrent blocks, i.e. if the design has multiple always blocks (see Listing 2.7), then all the always blocks will execute in parallel.

#### **Explanation Listing 2.6:**

The 'always' block is declared in Line 8, which begins and ends at Line 9 and 14 respectively. Therefore all the statements between Line 9 to 14 will execute sequentially and Quartus Software will generate the design based on the sequences of the statements. Any changes in the sequences will result in different design.

Note that, the output port 'eq' is declared as **reg** at Line 5. If we assign value to the signal inside the 'always' block then that signal must be declared as 'reg' e.g. value of 'eq' is assigned in Line 11 and 13, which are inside the 'always' block; hence 'eq' is declared as reg.

The 'always' keyword takes two arguments in Line 8 (known as 'sensitivity list'), which indicates that the process block will be executed if and only if there are some changes in 'a' and 'b'. '@' is used after 'always' for defining the sensitivity list. In Line 10-13, the 'if' statement is declared which sets the value of 'eq' to 1 if both the bits are equal (Line 10-11), otherwise 'eq' will be set to 0 (Line 12-13). Fig. 2.7 shows the design generated by the Quartus Software for this listing. '==' in Line 10 is one of the condition operators; whereas && is the logical operator, which are discussed in detail in Chapter 3.

Listing 2.6: Procedural assignment statement

```

comparator2BitProcedure.v

1

2

module comparator2BitProcedure(

3

4

input wire[1:0] a, b,

5

output reg eq

);

6

always @(a,b)

8

begin

9

if (a[0]==b[0] \&\& a[1]==b[1])

10

eq = 1;

11

else

12

eq = 0;

13

end

14

endmodule

15

```

Fig. 2.7: 2 bit comparator, Listing 2.6

#### 2.2.5 Mixed modeling

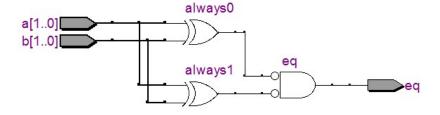

We can mixed all the modeling styles together as shown in Listing 2.7. Here two always blocks are used in Line 10 and 18, which is the 'procedural assignment statements'. Then in Line 26, 'continuous assignment statement' is used for assigning the value to output variable 'eq'.

#### **Explanation Listing 2.7**

Note that, output 'eq' is defined as 'wire' (as value to 'eq' is assigned using continuous assignment statement), whereas signals 's0' and 's1' is defined as 'reg' (as values are assigned using procedural assignment statement i.e. inside the 'always' block). Two always blocks are used here. Always block at Line 10 checks whether the LSB of two numbers are equal or not; if equal then signal 's0' is set to 1 otherwise it is set to 0. Similarly, the always block at Line 18, sets the value of 's1' based on MSB values. Lastly, Line 16 sets the output 'eq' to 1 if both 's0' and 's1' are 1, otherwise it is set to 0. The design generated for this listing is shown in Fig. 2.8.

Listing 2.7: Multiple procedural assignment statements

```

1

comparator 2Bit Mixed.v

2

3

module comparator2BitMixed(

4

input wire[1:0] a, b,

output wire eq

5

);

6

7

8

reg[1:0] s0, s1;

9

always @(a,b)

10

11

begin

if (a[0]==b[0])

12

s0 = 1;

13

else

14

s0 = 0;

15

end

16

17

always @(a,b)

18

begin

19

if (a[1]==b[1])

s1 = 1;

21

22

else

s1 = 0;

23

24

end

25

assign eq = s0 & s1;

26

endmodule

27

```

Fig. 2.8: 2 bit comparator, Listing 2.7

## 2.3 Conclusion

In this tutorial, various features of Verilog designs are discussed briefly. We designed the two bit comparator with four modeling styles i.e. Continuous assignment statement, Structural design, Procedural assignment statement and Mixed styles. Also, differences between the generated-designs with these four methods are shown.

2.3. Conclusion 26

What matters is to live in the present, live now, for every moment is now. It is your thoughts and acts of the moment that create your future. The outline of your future path already exists, for you created its pattern by your past.

-Sai Baba

# Chapter 3

# Data types

#### 3.1 Introduction

In the Chapter 2, we used the data-types i.e. 'wire' and 'reg' to define '1-bit' & '2-bit' input and output ports and signals. Also, some operators e.g. 'and (&)' and 'or (|)' etc. were discussed. In this chapter, some more information is provided on these topics.

#### 3.2 Lexical rules

Verilog is case sensitive language i.e. upper and lower case letters have different meanings. Also, Verilog is free formatting language (i.e. spaces can be added freely), but we use the python like approach to write the codes, as it is clear and readable. Lastly in Verilog, '//' is used for comments; also, multiline comments can written between /\* and \*/.

## 3.3 Data types

Data types can be divided into two groups as follows,

- **Net group**: Net group represents the physical connection between components e.g. wire, wand and wor etc. In the tutorials, we will use only one net data type i.e. 'wire', which is sufficient to create all types of designs.

- Variable group: Variable group represents the storage of values in the design. It is always used for the variables, whose values are assigned inside the 'always' block. Also, input port can not be defined as variable group, 'reg' and 'integer' are the example of variable group, which can be synthesized. We will use only 'reg' for designing purpose.

# 3.4 Logic values

Verilog has four logic values i.e. 0, 1, z and x as shown in Table 3.1,

Table 3.1: Logic values

| Logic | Description                                      |  |

|-------|--------------------------------------------------|--|

| 0     | logic '0' or false condition                     |  |

| 1     | logic '1' or true condition                      |  |

| Z     | high impedance state (used for tri-state buffer) |  |

| X     | don't care or unknown value                      |  |

## 3.5 Number representation

The number can be represented in various format as follows, which are listed in Table 3.2. Note that, 'reg' can be replaced with 'wire' in the table.

• Binary Format

```

reg [1:0] a = 2'b01; // number = 1; size = 2 bit;

reg [2:0] a = -3'b1; // unsigned number= -1 (in 2's complement form); size = 3 bit;

```

• Decimal Format

```

reg [3:0] a = 3'd1;  // number = 1; size = 3 bit;

reg [3:0] a = -3'd1;  // unsigned number = -1 (in 2's complement form); size = 3 bit;

reg [3:0] a = 1;  // unsigned number = 1; size = 4 bit;

reg [3:0] a = -1;  // unsigned number = -1; size = 4 bit in 2's complement form;

```

• Signed Decimal Form

```

integer a = 1; // signed number = 1; size = 32 bit;

integer a = -1; // signed number = -1; size = 32 bit in 2's complement form;

```

• For hexadecimal and octal representations use 'h' and 'o' instead of 'b' in binary format.

| Number                        | Value         | Comment                                              |

|-------------------------------|---------------|------------------------------------------------------|

| reg [1:0] a = 2'b01;          | 01            | b is for binary                                      |

| reg [1:0] $a = 2'b0001_1111;$ | 00011111      | _ is ignored                                         |

| reg [2:0] a = -3'b1;          | 111           | -1 in 2's complement with 3 bit (unsigned)           |

| reg [3:0] a = 4'd1;           | 0001          | d is for decimal                                     |

| reg [3:0] a = -4'd1;          | 1111          | -1 in 2's complement with 4 bit (unsigned)           |

| reg [5:0] a = 6'o12;          | 001_010       | o is for octal                                       |

| reg [5:0] b = 6'h1f;          | 0001_1111     | h is for hexadecimal                                 |

| reg [3:0] a = 1;              | 0001          | unsigned format                                      |

| reg [3:0] a = -1;             | 1111          | -1 in 2's complement with 4 bit (unsigned)           |

| reg signed [3:0] $a = 1$ ;    | 0001          | signed format                                        |

| reg signed [3:0] $a = -1;$    | 1111          | -1 in 2's complement with 4 bit (signed)             |

| integer $a = 1$ ;             | 0000_00000001 | 32 bit i.e. 31-zeros and one-1 (signed)              |

| integer $a = -1$ ;            | 1111_11111111 | -1 in 2's complement with 32 bit i.e. all 1 (signed) |

| reg [4:0] a = 5'bx            | XXXXX         | x is don't care                                      |

| reg [4:0] a = 5'bz            | ZZZZZ         | z is high impedance                                  |

| reg [4:0] a = 5'bx01          | xxx01         | z is high impedance                                  |

Table 3.2: Number representation

#### Note:

- 'wire' and 'reg' are in unsigned-format by default. These can be used for synthesis and simulation.

- 'integer' is in signed-format by default. This should be used for simulation.

# 3.6 Signed numbers

By default, 'reg' and 'wire' data type are 'unsigned number, whereas 'integer' is signed number. Signed number can be defined for 'reg' and 'wire' by using 'signed' keywords i.e. 'reg signed' and 'wire signed' respectively as shown in Table 3.2.

Also, 'signed numbers' can be converted into 'unsigned numbers' using '\$unsigned()' keyword e.g. if 'a = -3 (i.e. 101 in 2's complement notation)', then '\$unsigned(a)' will be '5 (i.e. value of 101)'. Similarly, 'unsigned numbers' can be converted into 'signed numbers' using 'signed()' keyword.

**Warning:** Although, numbers can be converted from one form to another, but it should be avoided as it may results in errors which are difficult to find.

## 3.7 Operators

In this section, various synthesizable operators of Verilog are discussed, which are shown in Table 3.3.

Symbol Description Type Note Arithmetic add subtract multiply divide may not synthesize modulus (remainder) may not synthesize power may not synthesize Bitwise not & and xor & or & nand mix two operators Relational greater than < less than >= greater than or equal less than or equal equal not equal != Logical ! negation logical OR && logical AND Shift operator right shift >> left shift <<>>> right shift with MSB shifted to right <<< same as << Concatenation Concatenation Replication "e.g.  $\{2\{3\}\} = \{33\}$ " { } } Conditional conditional e.g. (2>3) ? 1:0 Sign-format \$unsigned(-3) \$unsigned() signed to unsigned conversion unsigned to signed conversion \$signed() \$signed(3)

Table 3.3: Verilog operators

# 3.8 Arithmetic operator

Three arithmetic operators i.e. +, -, and \* can be synthesized in verilog.

#### 3.8.1 Bitwise operators

Four bitwise operator are available in verilog i.e. '&' (and), '|' (or), ' ^ ' (xor) and '~' (not). Further, we can combine these operators to define new operators e.g. '~&' or '&~' can be used as 'nand' operations etc.

3.7. Operators 29

#### 3.8.2 Relational operators

We already see the equality relational operation i.e. '==' in section Section 2.2.4. Further, five relational operators are defined in verilog i.e. '>', '>=', '<', '<=' and '!='(not equal to).

#### 3.8.3 Logical operators

We already see the 'and' relational operation i.e. '&&' in section Section 2.2.4. Further, three relational operators are defined in verilog i.e. '||' (or), '&&' and '!' (negation).

#### 3.8.4 Shift operators

Verilog provides 4 types of shif operators i.e. >>, <<, >>>, <<<. Let 'a = 1011-0011', then we will have following results with these operators,

- a >> 3 = 0001-0110 i.e. shift 3 bits to right and fill the MSB with zeros.

- a << 3 = 1001-1000 i.e. shift 3 bits to left and fill the LSB with zeros.

- a >>>3 = 1111-0110 i.e. shift 3 bits to right and fill the MSB with sign bit i.e. original MSB.

- a <<<3 = 1111-0110 i.e. same as a <<3.

#### 3.8.5 Concatenation and replication operators

Concatenation operation '{ }' is used to combine smaller arrays to create a large array as shown below,

```

wire[1:0] a = 2b'01;

wire[2:0] b = 3b'001;

wire[3:0] c;

assign c = {a, b} // c = 01001 is created using a and b;

```

Replication operator is used to repeat certain bits as shown below,

```

assign c = \{ 2\{a\}, 1'b0 \} // c = 01010 i.e. a is repeated two times i.e. 01-01

```

#### 3.8.6 Conditional operator

Conditional operator (?:) can be defined as follows,

```

assign c = (a>b) ? a : b; // i.e. c=a if a>b; else c=b;

```

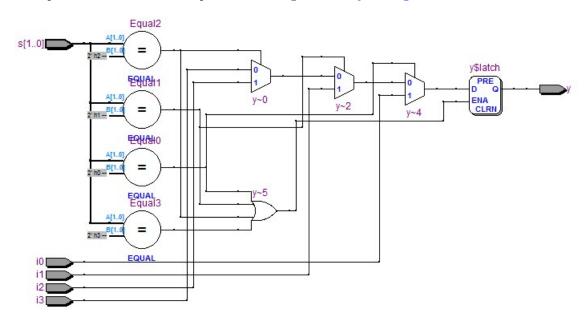

Also, conditional expression can be cascaded as shown in Listing 3.1, where 4x1 multiplexer is designed. Multiplexer is a combinational circuit which selects one of the many inputs with selection-lines and direct it to output. Fig. 3.1 illustrates the truth table for 4x1 multiplexer. Here 'i0 - i3' the input lines, whereas 's0' and 's1' are the selection line. Base on the values of 's0' and 's1', the input is sent to output line, e.g. if s0 and s1 are 0 then i0 will be sent to the output of the multiplexer.

Listing 3.1: Cascaded conditional operator

```

1  // conditionalEx.v

2

3  module conditionalEx(

4    input wire[1:0] s,

5    input wire i0, i1, i2, i3,

6    output wire y

7  );

8

9  assign y = (s == 2'b00) ? i0 : // y = i0 if s=00

```

(continues on next page)

| s0 | <b>s1</b> | У  |

|----|-----------|----|

| 0  | 0         | i0 |

| 0  | 1         | i1 |

| 1  | 0         | i2 |

| 1  | 1         | i3 |

Fig. 3.1: Truth table of 4x1 multiplexer

(continued from previous page)

```

(s == 2'b01) ? i1 : // y = i1 if s=01

(s == 2'b10) ? i2 : // y = i2 if s=10

(s == 2'b11) ? i3 : // y = i3 if s=11

y; // else y = y i.e. no change

endmodule

```

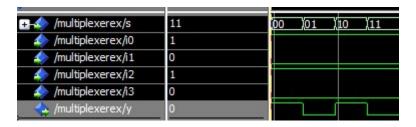

The design generated in Fig. 3.2 is exactly same as the design generated by 'if-else statement' which is discussed in Section 4.7. Therefore, Fig. 3.2 is described and compared with other designs in Section 4.7. Further, Fig. 3.3 shows the output waveform of the multiplexer which is generated by Listing 3.1.

Fig. 3.2: Multiplexer generated by Listing 3.1

#### 3.8.7 Parameter and localparam

Parameter and local param are used to create reusable codes along with avoiding the 'hard literals' from the code as shown in following section.

Fig. 3.3: Waveforms of Listing 3.1

#### 3.8.8 localparam

'localparam' keyword is used to defined the constants in verilog. In Listing 3.2, N is defined in line 8 with value 3. Then this value is used in line 10 and 11. Suppose we want to change the constant value to 4. Now, we need to change it only at one place i.e. line 8 (instead of changing everywhere in the code e.g. line 10 and 11 in this example). In this way, we can remove the hard literals from the codes.

Listing 3.2: Localparam

```

// constantEx.v

2

module constantEx(

3

input wire [3:0] a, b,

5

output wire [3:0] z

6

);

localparam N = 3, M = 2; //localparam

8

9

wire [N:0] x;

10

wire [2**N:0] y;

11

12

// use x and y here

13

assign z = a & b;

14

15

endmodule

16

```

• It is better to define the size of the local-parameters otherwise 32-bit signed-format will be used for the local parameters, as shown below

```

// 32-bit signed-format

localparam N = 3, M = 2;

// N & M are 5 bit and 3 bit unsigned numbers respectively

localparam N = 5'd3, M = 3'd2;

```

#### 3.8.9 Parameter and defparam

'localparam' can not be modified after declaration. But we can define the parameter in the module, which can be modified during component instantiation in structural modeling style as shown below.

#### **Explanation Listing 3.3**

In line 5, two parameters are defined i.e. 'N' and 'M'. Then ports 'a' and 'b' are defined using parameter 'N'. The always block (lines 13-19) compares 'a' and 'b' and set the value of 'z' to 1 if these inputs are equal, otherwise set 'z' to 0.

#### Listing 3.3: Parameter

```

// parameterEx.v

2

3

module parameterEx

#(

4

parameter N = 2, M = 3 //parameter

5

6

7

(

8

input wire [N-1:0] a, b,

9

output reg [N-1:0] z

10

);

11

12

always @(a,b)

13

14

begin

if (a==b)

15

z = 1;

16

else

17

z = 0;

18

end

19

endmodule

20

```

#### Explanation Listing 3.4 and Listing 3.5

In line 5, 'a' and 'b' are defined as 4-bit vector. Structural modeling is used in Line 9, where parameter mapping and port mapping is performed. Note that, in line 16, '.N(5)' will override the default value of N i.e. N=2 in Listing 3.3. Also, parameter 'M' is not mapped, therefore default value of M will be used, which is defined in Listing 3.3. In this way, we can remove 'hard literals' from the codes, which enhances the reusability of the designs. Value of the parameter 'N' can also be set using 'defparam' keyword, as shown in Listing 3.5.

Listing 3.4: Parameter instantiation

```

// parameterInstantEx.v

1

2

module parameterInstantEx

3

4

5

input wire [4:0] a, b,

6

output wire [4:0] z

);

parameterEx \#(.N(5)) compare4bit ( .a(a), .b(b), .z(z));

9

10

endmodule

11

```

Listing 3.5: Parameter instantiation using 'defparam'

```

// parameterInstantEx2.v

1

2

module parameterInstantEx2

3

4

input wire [4:0] a, b,

5

output wire [4:0] z

6

);

8

parameterEx compare4bit ( .a(a), .b(b), .z(z));

9

defparam compare4bit.N = 5; // 'defparam' to set the value of parameter

10

11

endmodule

12

```

• It is better to define the size of the parameters otherwise 32-bit signed-format will be used for the parameters,

as shown below

```

// 32-bit signed-format

parameter N = 2, M = 3

// N & M are 5 bit and 4 bit unsigned numbers respectively

parameter N = 5'd2, M = 4'd3;

```

## 3.9 Conclusion

In this chapter, we saw various data types and operators. Further Parameters and localparam are shown which can be useful in creating the reusable designs.

3.9. Conclusion 34

-Ramakrishna Paramahansa

## Chapter 4

# Procedural assignments

#### 4.1 Introduction

In Chapter 2, a 2-bit comparator is designed using 'procedural assignments'. In that chapter, 'if' keyword was used in the 'always' statement block. This chapter presents some more such keywords which can be used in procedural assignments.

## 4.2 Combinational circuit and sequential circuit

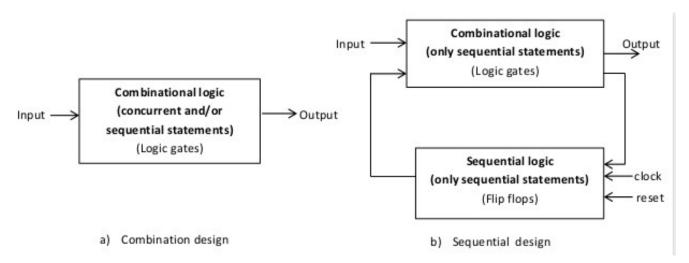

Digital design can be broadly categorized in two ways i.e. **combinational designs** and **sequential designs**. It is very important to understand the differences between these two designs and see the relation between these designs with various elements of Verilog.

- Combinational designs: Combinational designs are the designs in which the output of the system depends on present value of the inputs only. Since, the outputs depends on current inputs only, therefore 'no memory' is required for these designs. Further, memories are nothing but the 'flip flops' in the digital designs, therefore there is no need of 'flip flops' in combination designs. In the other words, only 'logic gates (i.e. and, not and xor etc.)' are required to implement the combinational designs.

- Sequential designs: Sequential designs are the designs in which the output depends on current inputs and previous states of the system. Since output depends on previous states, therefore 'memories' are required for these systems. Hence, in the sequential designs the 'flip flops' are needed along with the logic gates.

Fig. 4.1: Block diagram of 'combinational' and 'sequential' designs

## 4.3 Concurrent statements and sequential statements

In Listing 2.3, we saw that the concurrent statements execute in parallel, i.e. the order of the statement does not matter. Whereas Listing 2.6 shows the example of 'sequential statements' where the statements execute one by one. Following are the relationship between 'statements' and 'design-type',

- Please note that 'sequential statements' and 'sequential designs' are two different things. Do not mix these together.

- Combinational designs can be implemented using both 'sequential statements' and 'concurrent statements'.

- Sequential designs can be implemented using 'sequential statements' only.

- Sequential statements can be defined inside 'always' block only. Further, these blocks executes concurrently e.g. if we have more than one always block then these block will execute in parallel, but statements inside each block will execute sequentially.

- Sequential designs are implemented using various constructs e.g. 'if', 'case' and 'for' etc., which are discussed in this chapter.

- Conditional operator (?:) can be used for combinational designs.

Note: Remember: (see the words 'design', 'logic' and 'statement' carefully)

- Only 'logic gates (i.e. and, not and xor etc.)' are required to implement the combinational designs.

- Both 'logic gates' and 'flip flops' are required for implementing the sequential designs.

- Lastly, the 'sequential design' contains both 'combinational logics' and 'sequential logics', but the combinational logic can be implement using 'sequential statements' only as shown in Fig. 4.1; whereas the 'combination logic' in the combinational designs can be implemented using both 'concurrent' and 'sequential' statements.

## 4.4 'always' block

All the statements inside the always block execute sequentially. Further, if the module contains more than one always block, then all the always blocks execute in parallel, i.e. always blocks are the concurrent blocks.

Note: Note that, we can write the complete design using sequential programming (similar to C, C++ and Python codes). But that may result in very complex hardware design, or to a design which can not be synthesized at all. The best way of designing is to make small units using 'continuous assignment statements' and 'procedural assignment statements', and then use the structural modeling style to create the large system.

## 4.5 Blocking and Non-blocking assignment

There are two kinds of assignments which can be used inside the always block i.e. blocking and non-blocking assignments. The '=' sign is used in blocking assignment; whereas the '<=' is used for non-blocking assignment as shown in Listing 4.1 and Listing 4.2. Both the listings are exactly same expect the assignment signs at lines 13-14. Due to different in assignment signs, the design generated by these listings are different as shown in Fig. 4.2 and Fig. 4.3, which are explained below.

#### **Explanation Listing 4.1**

In line 10, value of input port 'x' is assigned to output 'z'. Since, the value of 'z' is equal to 'x', therefore line 11 will be equivalent to 'z = x + y'; due to this reason, the design is generated as 'and' gate with inputs 'x' and 'y' as shown in Fig. 4.2.

Listing 4.1: Blocking assignment, Fig. 4.2

```

blockAssignment.v

1

2

module blockAssignment(

3

input wire x, y,

4

output reg z

5

);

6

always @(x,y)

8

9

begin

z = x; // since z = x

10

z = z \& y; // therefore, z = x + y;

11

12

endmodule

13

```

Fig. 4.2: Blocking assignment, Listing 4.1

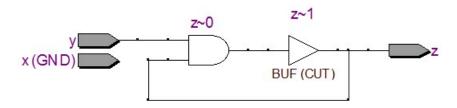

Fig. 4.3: Non-blocking assignment, Listing 4.2

#### **Explanation Listing 4.2:**

In non-blocking assignment, updated values inside the block are not used for assignment.} In line 10, value of input port 'x' is assigned to the 'z'. Since updated value inside the block are not used in non-blocking assignment, therefore in line 11, 'z = z & y;', the old value of 'z' will be used for assignments (instead of z=x); hence a feedback path is used in Fig. 4.3. Also, 'x' has no effect on the design as it is updating 'z' inside the block, which will not be used by non-blocking assignment; hence 'x' is not connected (i.e. connected to ground) in the design as shown in Fig. 4.3.

Listing 4.2: Non-blocking assignment, Fig. 4.3

```

// nonblockAssignment.v

1

2

module nonblockAssignment(

3

input wire x, y,

4

output reg z

5

6

always @(x,y)

8

begin

9

z \le x; // z_new = x

10

z \le z \& y; // z_new = z_entry + y (not z = z_new + y)

11

end

12

endmodule

13

```

**Note:** The block and non-blocking assignments can not be used together for a signal. For example, the below assignment will generate error as both 'blocking' and 'non-blocking' assignments are used for 'z',

```

z = x; // blocking assignment

z <= z & y; // non-blocking assignment</pre>

```

## 4.6 Guidelines for using 'always' block

The general purpose 'always' block of Verilog can be misused very easily. And the misuse of this block will result in different 'simulation' and 'synthesis' results. In this section, the general guidelines are provided for using the 'always' block in different conditions.

Further, we can use the specilialized 'always' blocks of SystemVerilog to avoid the ambiguities in synthesis and simulation results, which are discussed in Section 10.4.

**Note:** Note that, the 'always' block is used for 'synthesis (i.e. with sensitive list)' as well as 'simulation (i.e. with and without sensitive list)', which have different set of semantic rules. If we do not follow the below guidelines in the designs, then simulation and synthesis tools will infer different set of rules, which will result in differences in synthesis and simulation results.

Further, SystemVerilog has specialized 'always blocks' for different types of designs (see Section 10.4), which can catch the errors when the designs are not created according to below rules.

#### 4.6.1 'always' block for 'combinational designs'

Follow the below rules for combinational designs,

- Do **not** use the 'posedge' and 'negedge' in sensitive list.

- Sensitive list should contain all the signals which are read inside the block.

- No variable should be updated outside the 'always' block.

- Use blocking assignment (i.e. = ) for assigning values.

- All the variables should be updated for all the possible input conditions i.e. if-else and case statements should include all the possible conditions; and all the variables must be updated inside all the conditions.

#### 4.6.2 'always' block for 'latched designs'

Follow the below rules for latched designs,

- Do **not** use the 'posedge' and 'negedge' in sensitive list.

- Sensitive list should contain all the signals which are read inside the block.

- No variable should be updated outside the 'always' block.

- Use blocking assignment (i.e. = ) for assigning values.

- At least one the variables should **not** be updated for some of the possible input conditions.

#### 4.6.3 'always' block for 'sequential designs'

Follow the below rules for sequential designs,

- Use either 'posedge' or 'negedge' (not both) in sensitive list for all the elements.

- No variable should be updated outside the 'always' block.

- Use non-blocking assignment (i.e.  $\leq$  ) for assigning values.

#### 4.7 If-else statement

In this section, a 4x1 multiplexed is designed using If-else statement. We already see the working of 'if' statement in the Chapter 2. In lines 11-24 of Listing 4.3, 'else if' and 'else' are added to 'if' statement. Note that, If-else block can contain multiple 'else if' statements between one 'if' and one 'else' statement. Further, 'begin - end' is added in line 12-15 of Listing 4.3, which is used to define multiple statements inside 'if', 'else if' or 'else' block. Fig. 4.5 shows the waveform generated by Modelsim for Listing 4.3.

Note that, we are generating the exact designs as the VHDL tutorials, therefore line 22-23 are used. Also, we can remove the line 22-23, and change line 20 with 'else', which will also work correctly.

Fig. 4.4: Multiplexer using if statement, Listing 4.3

Listing 4.3: Multiplexer using if statement

```

// ifEx.v

2

module ifEx(

3

input wire[1:0] s,

4

input wire i0, i1, i2, i3,

5

output reg y

6

);

7

always @(s)

9

10

begin

if (s==2'b00)

11

begin //begin-end is required for more than one statements

12

y = i0;

13

// more statements

14

end

15

else if (s==2'b01)

16

y = i1;

17

else if (s==2'b10)

18

y = i2;

19

else if (s==2'b11)

20

21

y = i3;

22

else

y = y; // no change

23

24

end

25

```

(continues on next page)

4.7. If-else statement 39

endmodule

Fig. 4.5: Waveforms of Listing 4.3 and Listing 4.4

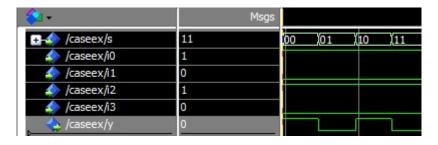

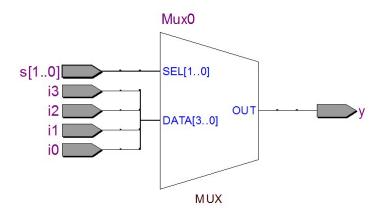

#### 4.8 Case statement

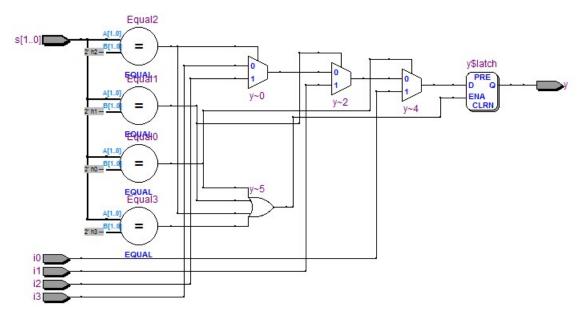

Case statement is shown in lines 11-16 of Listing 4.4. 's' is used in case statement at line 11; whose value is checked using 'when' keyword at lines 12 and 13 etc. The value of the output y depends on the value of 's' e.g. if 's' is '1', then line 12 will be true, hence value of 'i1' will be assigned to 'y'. Note that, we can use 'integer' notation (line 12) as well as 'binary' notation (line 13) in 'case' and 'if' statements. Design generated by Listing 4.4 is shown in Fig. 4.6.

Listing 4.4: Multiplexer using case statement

```

// caseEx.v

2

module caseEx(

input wire[1:0] s,

input wire i0, i1, i2, i3,

5

output reg y

6

);

7

always @(s)

9

begin

10

11

case (s)

12

0 : y = i0;

2'b01 : y = i1;

13

2 : y = i2;

14

3 : y = i3;

15

endcase

16

end

17

endmodule

18

```

We need not to define all the possible cases in the 'case-statement', the 'default' keyword can be used to provide the output for undefined-cases as shown in Listing 4.5. Here, only two cases are defined i.e. 7 and 3; for the rest of the cases, the default value (i.e. i2) will be sent to the output.

Listing 4.5: Case-statement with default values

```

module caseEx2(

input wire[2:0] s,

input wire [1:0] i0, i1, i2,

output reg [1:0] y

);

```

(continues on next page)

4.8. Case statement 40

Fig. 4.6: Multiplexer using case statement, Listing 4.4

```

always @(s)

9

begin

10

case (s)

11

7 : y = i0; // 7

12

3 : y = i1; // 3

13

default : y = i2; // 0, 1, 3, 4, 5

14

endcase

15

end

16

endmodule

17

```

## 4.9 Problem with Loops

Verilog provides two loop statements i.e. 'for' loop and 'while' loop'. These loops are very different from software loops. Suppose 'for i=1 to N' is a loop', then, in software 'i' will be assigned one value at time i.e. first i=1, then next cycle i=2 and so on. Whereas in Verilog, N logics will be implement for this loop, which will execute in parallel. Also, in software, 'N' cycles are required to complete the loop, whereas in Verilog the loop will execute in one cycle.

**Note:** As loops implement the design-units multiple times, therefore design may become large and sometimes can not be synthesized as well. If we do not want to execute everything in one cycle (which is almost always the case), then loops can be replaced by 'case' statements and 'conditional' statements as shown in section Section 4.10. Further, due to these reasons, we do not use loops in the design, and hence these are not discussed in the tutorial.

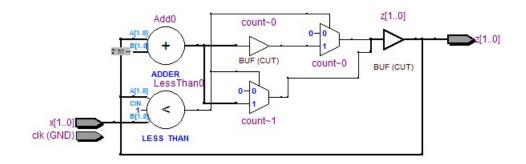

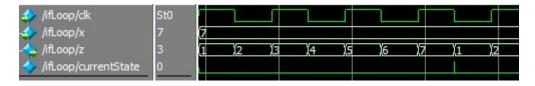

## 4.10 Loop using 'if' statement

In Listing 4.6, a loop is created using 'if' statement, which counts the number upto input 'x'.

#### **Explanation Listing 4.6**

In the listing, two 'always' blocks are used i.e. at lines 20 and 33. The process at line 20 checks whether the signal 'count' value is 'less or equal' to input x (line 22), and sets the currentState to 'continueState'; otherwise if count is greater than the input x, then currentState is set to 'stopState'.

Then next 'always' statement (line 33), increase the 'count' by 1, if currentState is 'continueState'; otherwise count is set to 0 for stopState. Finally count is displayed at the output through line 41. In this way, we can implement the loops using the 'always' statements.

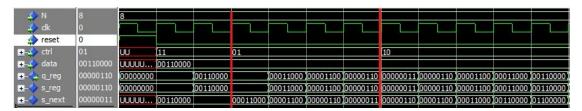

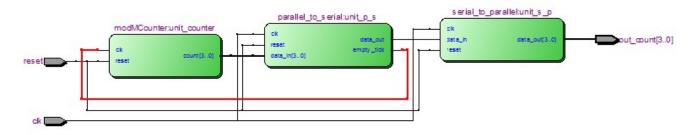

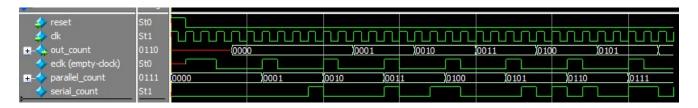

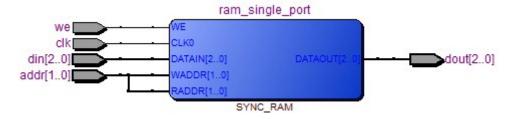

Fig. 4.7 shows the loop generated by the listing with parameter N=1. Further, Fig. 4.8 shows the count-waveforms generated by the listing with parameter N=3.