组合逻辑中的3:8译码器

- 掌握38译码器的基本原理

- 掌握组合逻辑的设计

- 掌握case的基本语法

- 使用拨码开关实现译码器输入功能

- 基于小脚丫STEP FPGA的拨码开关输入,LED输出实现38译码器功能

1. 知识点

译码器的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另外一个代码。

38译码器由三路信号输入,八路信号输出的译码器(2^3 = 8)。

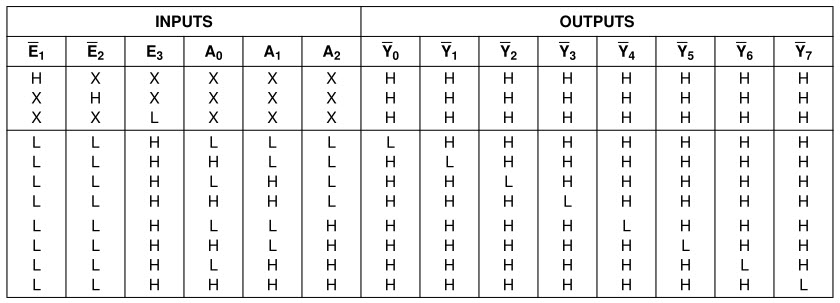

以芯片74HC138为例:

由上图芯片使能由E1,E2,E3共同控制

三路信号输入:A0,A1,A2

八路信号输出:Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7

由上图芯片使能由E1,E2,E3共同控制

三路信号输入:A0,A1,A2

八路信号输出:Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7

2. 原理图

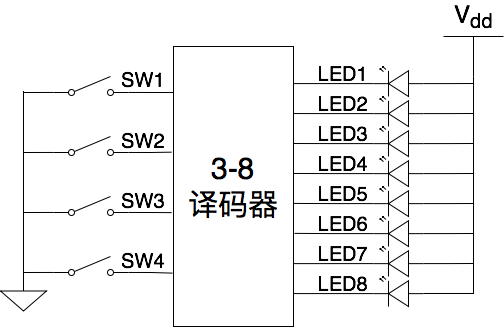

结合74HC138的结构原理及小脚丫FPGA的硬件配置,我们使用:

- 一个拨码开关(S1)替代E1、E2和E3的逻辑运算结果,作为芯片使能管脚

- 三个拨码开关(S2、S3、S4)作为38译码器的三路信号输入管脚

- 八个LED灯作为38译码器的八路信号输出管脚

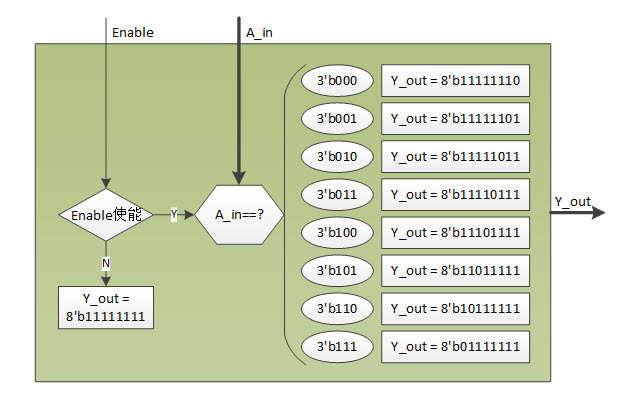

通过38译码器的原理及程序设计框图,我们不难发现这是一个比较简单的组合逻辑设计。

正如我们在原理及硬件连接中描述的,我们需要一路芯片使能端口、三路信号输入端口和八路信号输出端口。模块端口设计如下:

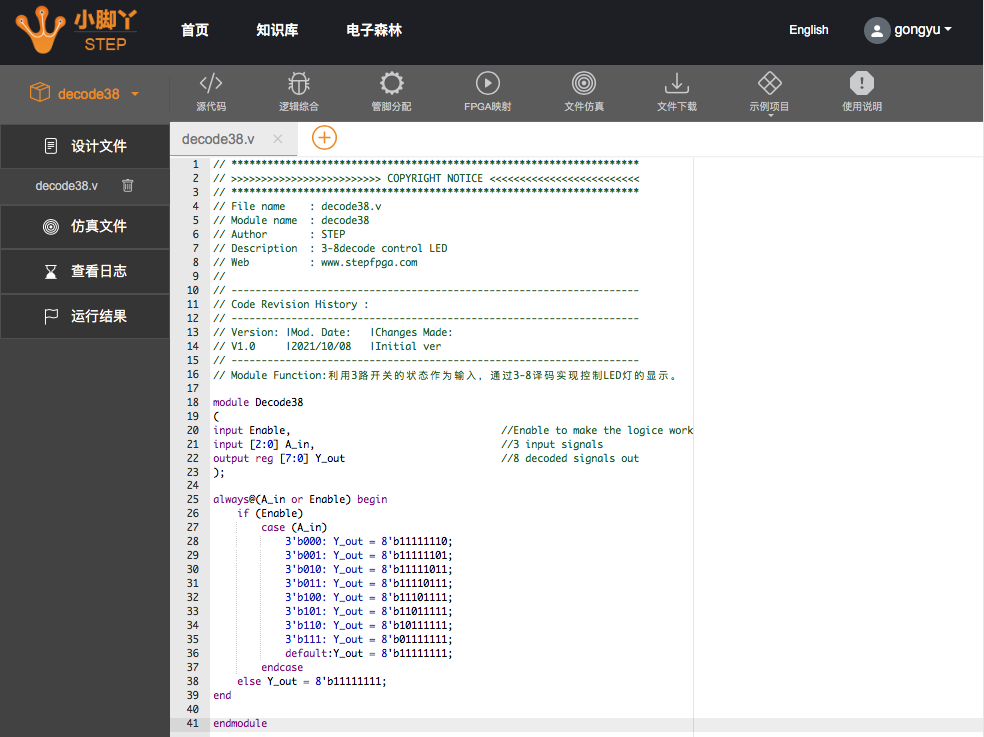

3. Verilog代码

// ******************************************************************** // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // ******************************************************************** // File name : decode38.v // Module name : decode38 // Author : STEP // Description : 3-8decode control LED // Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2021/10/08 |Initial ver // -------------------------------------------------------------------- // Module Function:利用3路开关的状态作为输入,通过3-8译码实现控制LED灯的显示。 module Decode38 ( input Enable, //Enable to make the logice work input [2:0] A_in, //3 input signals output reg [7:0] Y_out //8 decoded signals out ); always@(A_in or Enable) begin if (Enable) case (A_in) 3'b000: Y_out = 8'b11111110; 3'b001: Y_out = 8'b11111101; 3'b010: Y_out = 8'b11111011; 3'b011: Y_out = 8'b11110111; 3'b100: Y_out = 8'b11101111; 3'b101: Y_out = 8'b11011111; 3'b110: Y_out = 8'b10111111; 3'b111: Y_out = 8'b01111111; default:Y_out = 8'b11111111; endcase else Y_out = 8'b11111111; end endmodule

WebIDE里的代码界面