设计要求

基于小脚丫FPGA开发板和Nokia5110液晶屏实现数字时钟的设计,要求:

- 采用FPGA+按键+液晶屏实现数字时钟功能;

- 时间显示格式:XX:XX:XX (时:分:秒),采用24小时制;

- 增加按键控制,时分秒三位分别可调,处于调节状态的位闪烁区别;

硬件连接

FPGA的系统时钟来自于小脚丫FPGA开发板配置的24MHz时钟晶振,连接FPGA的C1引脚。

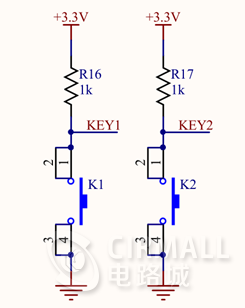

本设计用到两个按键K1和K2,硬件设计如图1所示,两个按键分别连接到FPGA的A2和B7引脚。

小脚丫FPGA开发板的控制按键

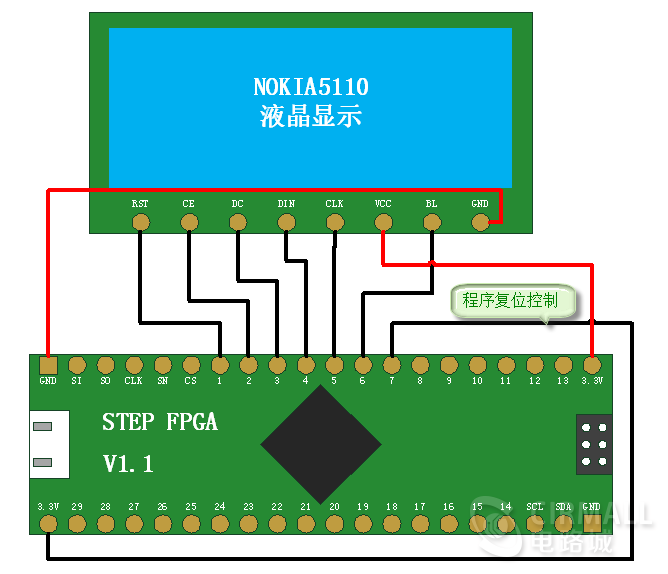

设计中需要驱动Nokia5110液晶屏作为显示,液晶屏与小脚丫FPGA开发板之间的连接关系如图2所示,对应的管脚如下。

| 液晶屏 | RST | CE | DC | DIN | CLK | VCC | BL | GND |

|---|---|---|---|---|---|---|---|---|

| FPGA | N3 | P2 | N2 | M1 | K1 | 3.3V | J1 | GND |

小脚丫FPGA开发板和5110液晶屏的连接

工作原理

- 使用计数器做分频处理,得到周期为1秒的脉冲信号secclk; - 使用三个8bit的BCD码表示时钟、分钟、秒钟的值,其中高4bit表示值的十位,低4bit表示值的个位; - 正常运行时,每来一个secclk秒钟个位加1,个位满10清零同时十位加1,当秒钟满60清零同时分钟个位加1,依次进行…直到23:59:59的下一刻全部清零;

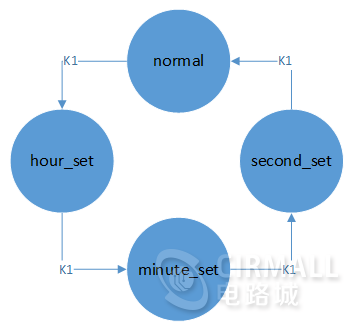

- 按键K1,模式调节,设计共分4中模式(运行模式、时针调节、分针调节、秒针调节),按动K1依次切换模式;

- 按键K2,时间调节,当数字时钟在时针调节、分针调节或秒针调节模式时,按动K2调节对应时间位;

- 硬件连接图中,程序复位控制线控制程序复位,断开重连设计复位。

代码设计

为了实现所需要的功能,我们将整个设计划分不同的模块,如图3所示。

数字时钟程序框架

4.1 clockctl模块

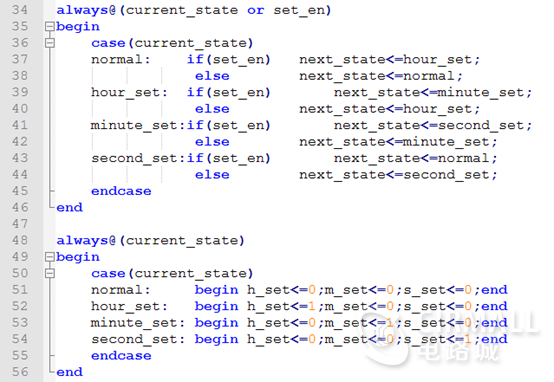

Clockctl模块主要实现数字时钟的模式控制,本设计共有4种模式(normal、hourset、minuteset、secondset)当K1按键按下(seten为高电平)时依次跳转,如图4所示。

状态控制

控制代码

4.2 clockcnt模块

Clockcnt模块主要实现时钟逻辑模块:

1)当处于normal模式时,每来一个secclk秒钟个位加1,个位满10清零同时十位加1,当秒钟满60清零同时分钟个位加1,依次进行…直到23:59:59的下一刻全部清零。

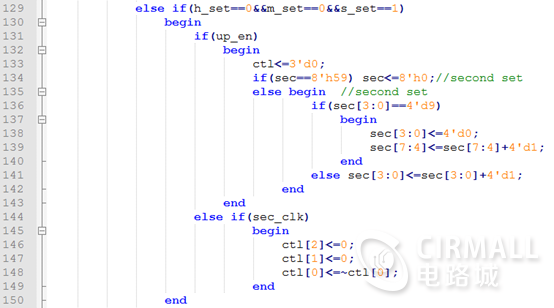

2)当处于secondset模式时,每次K2按键按下(upen为高电平)时,秒钟个位加1,个位满10清零同时十位加1,当秒钟满60清零,分钟和时钟保持不变,如下:

计数模块

系统实际运行

视频地址: http://v.youku.com/v_show/id_XMTM5MDE4OTE2MA==.html?from=s1.8-1-1.2 ====资源报告==== ^资源 |数量 |比例 | ^LUTs |718 |56% | ^寄存器 |179 |11% | ^存储器 |0 |0% | ^IO管脚 |12 | | ^时钟频率 |25MHz | | ====知识点==== - 时钟计数,分频 - 按键消抖处理 - 串行/并行转换 - Nokia5110液晶屏驱动 ====参考文档==== * Lattice MachXO2数据手册 * Nokia5110液晶屏资料 ====相关文件==== ^文件名称 | 功能| ^Digitalclock.v |顶层模块,将所有功能模块接口连接起来|

| Clockdiv.v |实现分频,产生按键、显示和秒时钟| ^keyboard.v | 实现按键消抖 |

|---|---|

| clockctl.v |实现数字时钟的模式控制| ^clockcnt.v | 时钟逻辑,产生时分秒的数值 |

| LCD_nokia5110.v | 驱动Nokia5110液晶屏的显示 |