点亮一颗LED

在这个示例中,我们先以点亮FPGA核心板上的任意一个LED为例,看一下LED的工作原理以及小脚丫FPGA上的LED的配置,Verilog的基本语法。

1. 知识点

- LED的工作原理

- Web IDE的使用

- FPGA管脚的配置和使用

- FPGA的设计流程 - 从创建项目到下载代码

- Verilog的基本语法结构

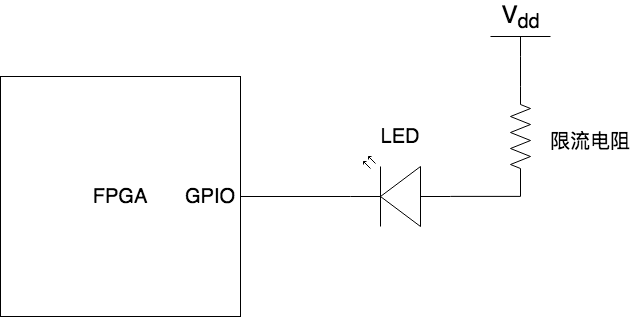

2. 原理图

从这个图中可以看出,如果连接该LED的FPGA的IO管脚是高电平(在Verilog代码中设置为1‘b1),LED两端都是高电平,无电流通过LED,将连接该LED的FPGA的IO管脚电平拉低(在Verilog代码中设置为1‘b0),LED两端的压差让电流流过,流过的电流取决于限流电阻的大小: I =(3.3V - Vfd)/ R 其中Vfd为LED的前向电压,可见要点亮LED,供电电压必须超过Vfd才行,多数LED的Vfd在1.7V-1.8V左右,用1.2V的电压来直接驱动LED是不可能的。 电流的大小会影响LED的亮度,对于同一颗LED,限流电阻变大,会让LED的亮度变暗,限流电阻变小,LED的亮度会变大,在本核心板上,LED的限流电阻都为1kΩ。

LED的亮度也取决于其工艺和材料,这个需要查阅生产厂商提供的数据。

总之,要让LED亮,就要把对应的IO管脚设置为低电平。

3. Verilog代码

根据Web IDE的使用流程介绍,我们先创建一个工程,并在该工程里面创建一个.v的代码(.v表示verilog的代码,代码名字跟工程的名字不需要一致):

module one_led_on(led); output led; assign led = 1'b0; endmodule

这段代码可以说是最简单的一段Verilog程序了,从这段程序中可以看出Verilog语言的基本结构

- 以module(模块)开始,endmodule结束的一段程序为描述某一项功能的基本单元,类似基于对象编程软件里面的“类”,写一次可以被多次调用。简单的设计可能只需要一个module来包含所有的逻辑功能,复杂的设计可能就需要多个module,它们通过module的端口信号互相连接起来,它们可以并行执行。模块化的好处就是你可以直接调用别人封装好的module来使用;

- 每个模块都有其名字,建议用贴切含义的英文来命名(比如本示例里面的oneledon),可读性强,也不会出现莫名其妙的编译错误;

- 每个模块都有用()包裹起来的端口 - 跟其它模块或FPGA的外围电路打交道的输入输出信号,在本示例只用了一个端口led,因此()中只有一个端口的名字;

- 对每一个端口的属性进行定义 - 是输入还是输出,如果是内部信号,它们是导线wire类型,还是存储器reg类型? 在这里只用了一个输出端口led,对其属性“output”进行了定义,指定其为输出信号;

- 定义完端口,就开始逻辑的主体,在这里也很简单,只是让led这个管脚信号为低电平,使用连续赋值的assign语句 - assign led = 1'b0, 1’b0表示为一位的数字,而且值为“0”。从电路结构角度讲,每个连续赋值语句对应一个子模块,其左侧的变量表示为电路的输出,右侧的逻辑表达式为电路需要执行的逻辑操作。

4. 管脚分配

点击Web IDE的第二个功能键“逻辑综合”,系统会自动将你写好的Verilog代码进行综合,如果没有语法错误,则给你一个Success的信息,你就可以走到下一步 - “管脚分配”了。 我们的Web IDE会根据你写好的module自动提取输入输出管脚的名字,你只要使用鼠标,通过图形化的界面将这些module里的端口信号的名字映射到相应的管脚上即可,在这里我们将led映射到板子上的第三个led,鼠标指向led3,其右侧会弹出一个向下的箭头,点击该箭头,就可以看到led的名字了(如果多个端口还没有分配管脚,这些未分配的端口信号的名字会出现在列表中),选中led,完成映射

在“管脚分配”里将第三颗LED配置为亮 (ON),分配了管脚的地方会亮起来

点击“FPGA映射”,系统会自动根据你分配好的管脚执行,生成JED文件,如果没有错误,会列出一堆的信息后,告诉你生成了jed的文件,在这段信息中也会有详细的资源使用报告,这些资源报告的信息也是很重要的,为完成同样一个功能,不同的人写出来的逻辑占用的资源也是不同的。