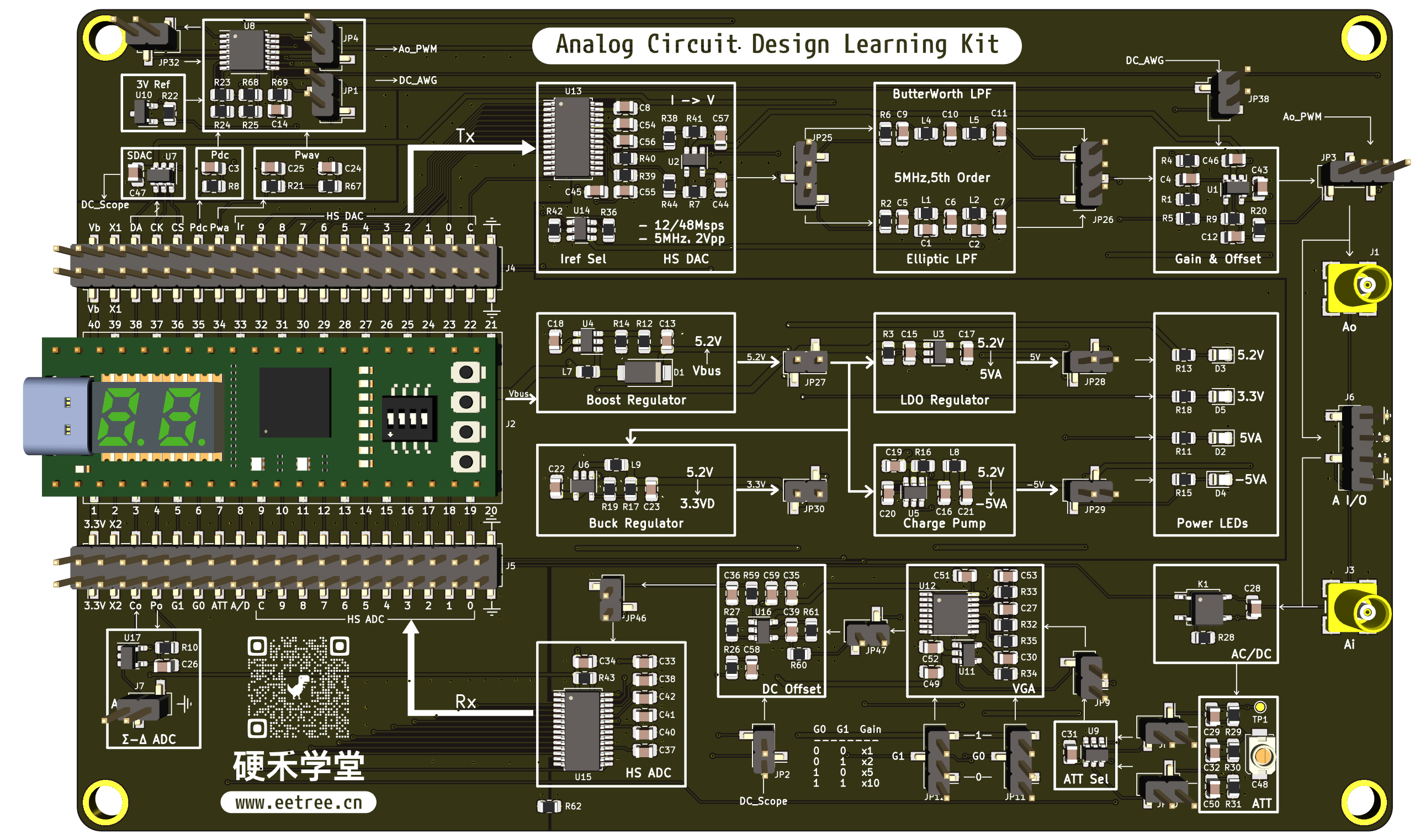

基于FPGA的虚拟仪器 - 模拟/数字系统学习/实训平台

这是一套专为模拟电路工程化设计学习而设计的学习、训练套件,基于小脚丫FPGA做核心控制,涵盖了模拟电路的主要知识点。

设计目标:

设计目标:

- 学习模拟电路的系统设计

- 高速数据采集的知识点和系统设计

- 高速任意信号发生器的知识点和系统设计

- 基于USB供电的电源知识点学习和设计

- 学习FPGA逻辑编程

- 学习模拟/数字混合系统设计

- 学习用仪器尤其是口袋仪器ADALM2000来观察、调试模拟、数字信号

- 学习各种元器件的焊接调试方法,板上所有电阻、电容、电感都采用0805封装,方便手工焊接,搭配其它SMD器件,可以让学习者从头开始自己焊接、调试最终组成一个完整的系统

- 灵活搭配其它外设配件 - 按键、显示屏、传感器、电机等,构成灵活多样的系统。

学习辅助工具

1 主要功能

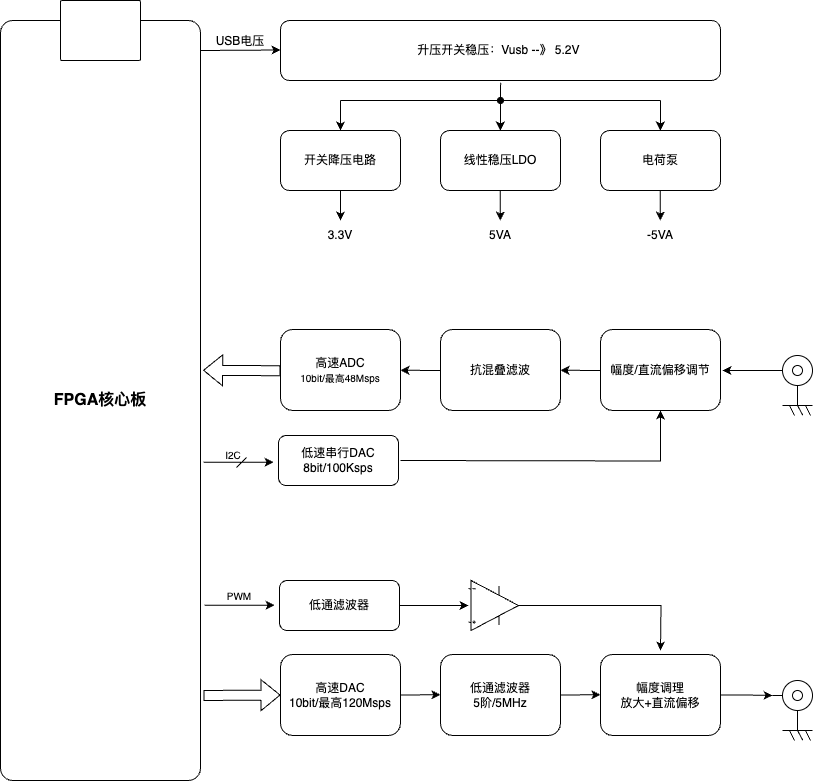

1.1 核心控制部分:

1.2 信号产生部分

- 板上使用了最高120Msps/10位的高速DAC可用于任意信号发生器

- 使用小脚丫Web IDE工作在12MHz主频,查看生成模拟信号的频谱以及模拟滤波器的作用

- 使用Diamond/Quartus工具可以通过锁相环让高速DAC工作在最高120Msps转换率,查看生成模拟信号的频谱以及模拟滤波器的作用

- 板上两种5阶低通滤波器,截止频率设定为5MHz,可以通过跳线选择其中一种,并进行对比,可以使用ADALM2000的网络分析功能查看两个低通滤波器网络的特性

- 五阶的巴特沃斯低通滤波器

- 五阶的椭圆低通滤波器

- 信号幅度控制电路

- 模拟开关切换DAC的参考电流,有x4的扩展,搭配10bit的高速DAC,能够得到72dB的动态范围,相当于使用了12位的高速DAC

- 输出级运算放大器固定增益

- 直流偏移调节

1.3 数据采集部分

- 板上有最高50Msps转换率/10位精度的高速ADC

- 使用Web IDE只支持板上12MHz的时钟频率,高速ADC工作在12Msps

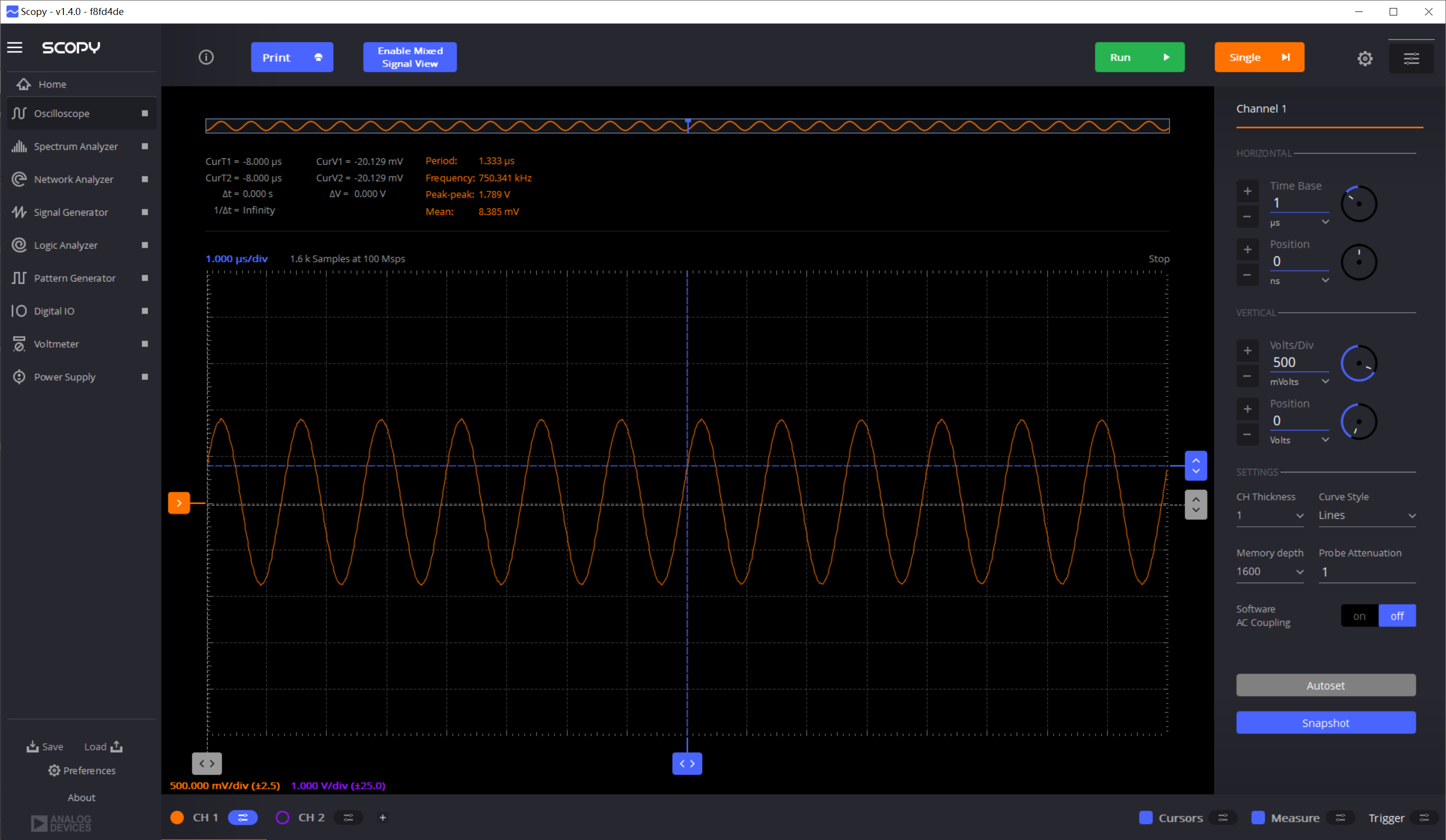

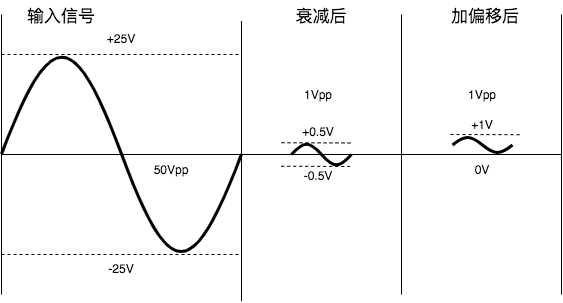

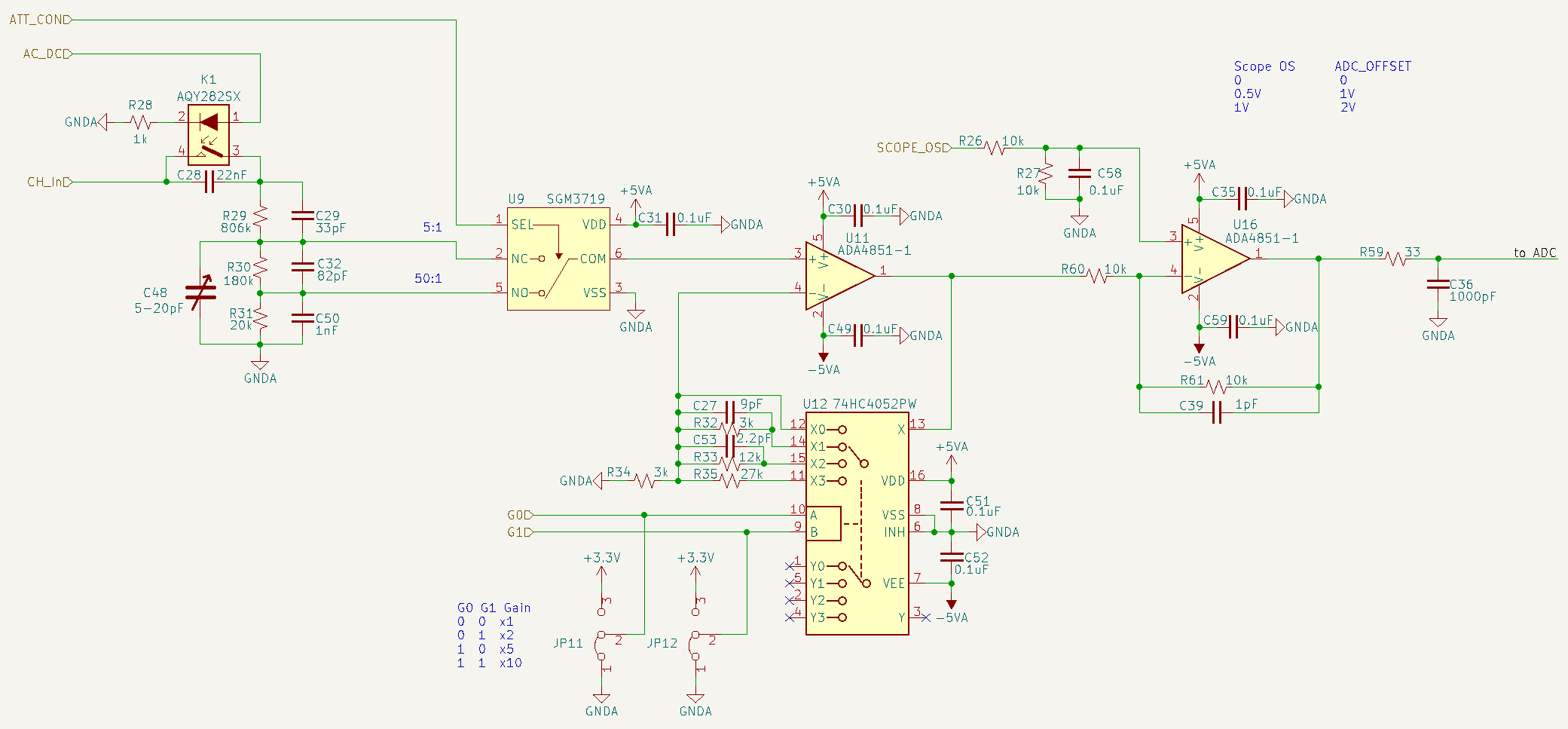

- 模拟信号调理电路

- 输入信号衰减 - 5:1和50:1两种

- 模拟开关选择 - 从两种衰减中进行选择

- 可编程信号放大 - 通过模拟开关选择不同的反馈电阻,从而产生不同的增益

- 抗混叠滤波器 - 简单的一阶低通滤波器

- 直流偏置电压添加 - 满足ADC的模拟信号输入的范围

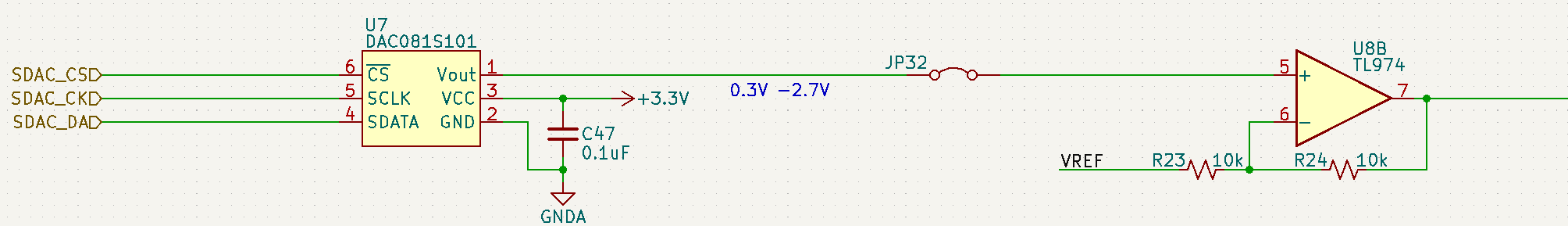

1.4 低速串行DAC

用于产生直流电压,控制ADC的直流偏置电压

1.5 通过PWM产生直流电压

用于控制DDS信号发生器的输出直流电压,同串行DAC的性能进行比较

- 纹波

- 成本

1.6 通过PWM产生任意信号

产生DDS 任意波形,同高速DAC生成的任意信号进行比较

1.7 通过FPGA + 高速比较器构成Sigma Delta ADC

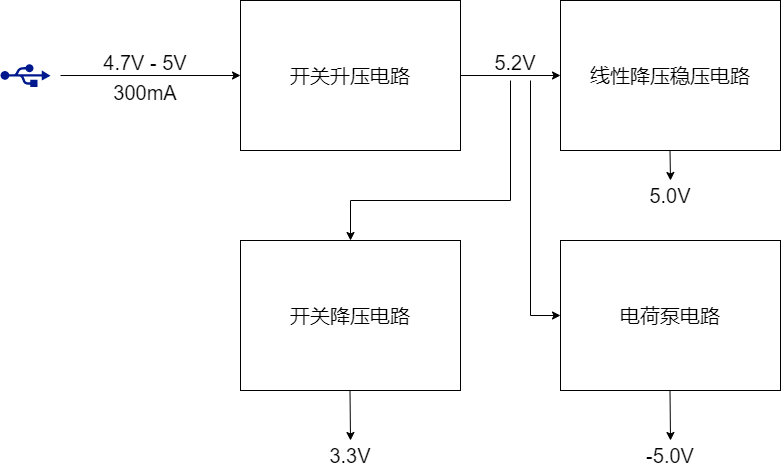

1.8 电源变换部分

- 输入USB电压(5V) 转5.2V升压电路

- 5.2V转5V线性LDO电路

- 5.2V转-5V电荷泵电路

- 5.2V转3.3V开关降压电路

- 电压指示电路LED

1.9 数字外设扩展

小脚丫核心模块的40根管脚可以都通过跳线同板上的其它功能进行连接。这给予了我们一定的灵活性,我们可以在某些板上功能不用的是情况下,使用它们空余出来的管脚通过杜邦线来连接外部的扩展功能。比如可以连接外部的显示屏、传感器、按键、编码器等等:

- 构成单通道信号发生器 - 将连接高速ADC的数字IO用来连接LCD屏、按键或旋转编码器就可以构成一个完整的可以控制参数、可以显示参数乃至波形的信号发生器系统

- 构成单通道示波器 - 将连接高速DAC的数字IO来连接LCD屏、按键或旋转编码器就可以构成一个完整的可以控制界面、显示波形、显示采集到的波形参数的数字示波器系统。

2 PCB设计

2.1 框图

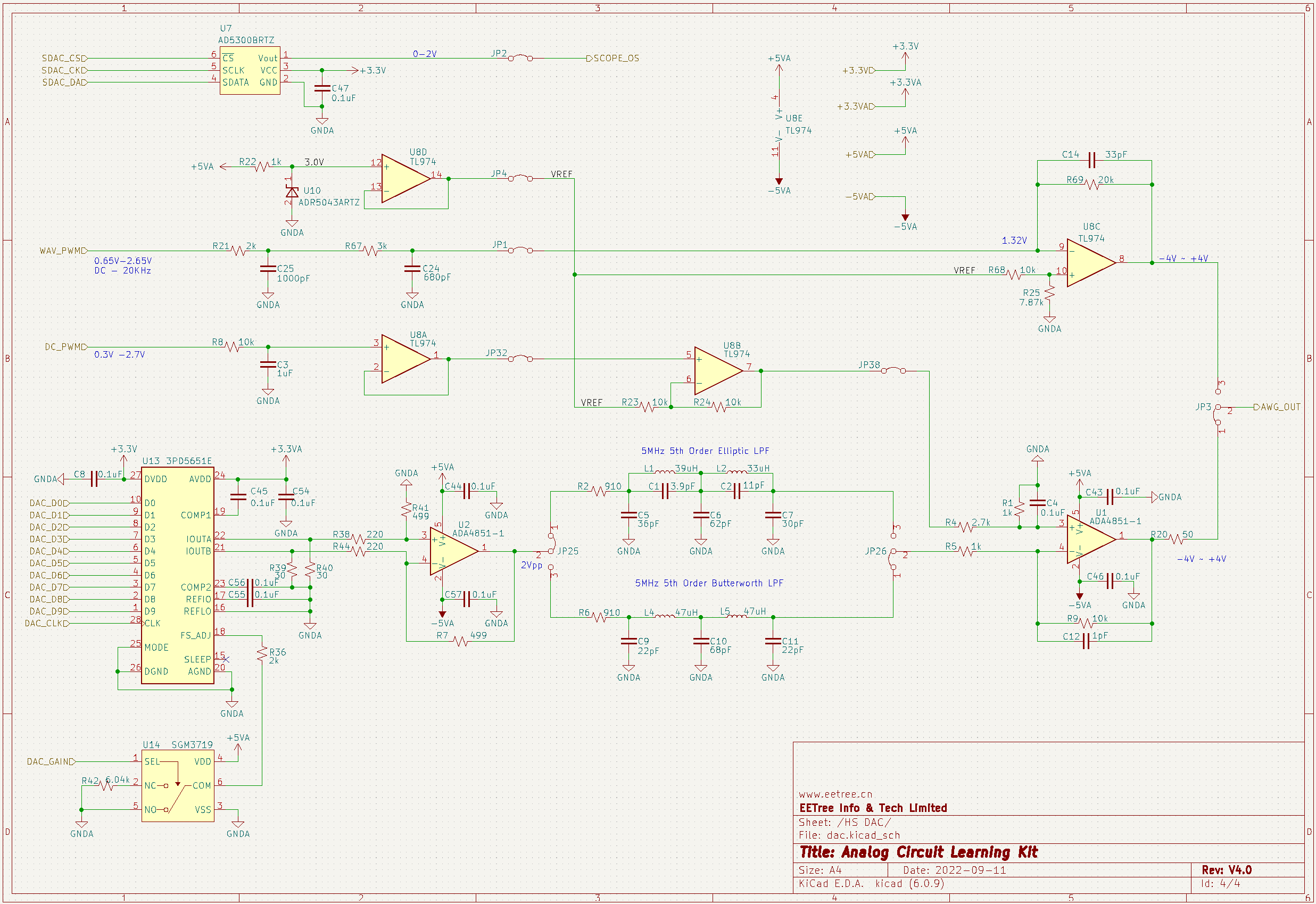

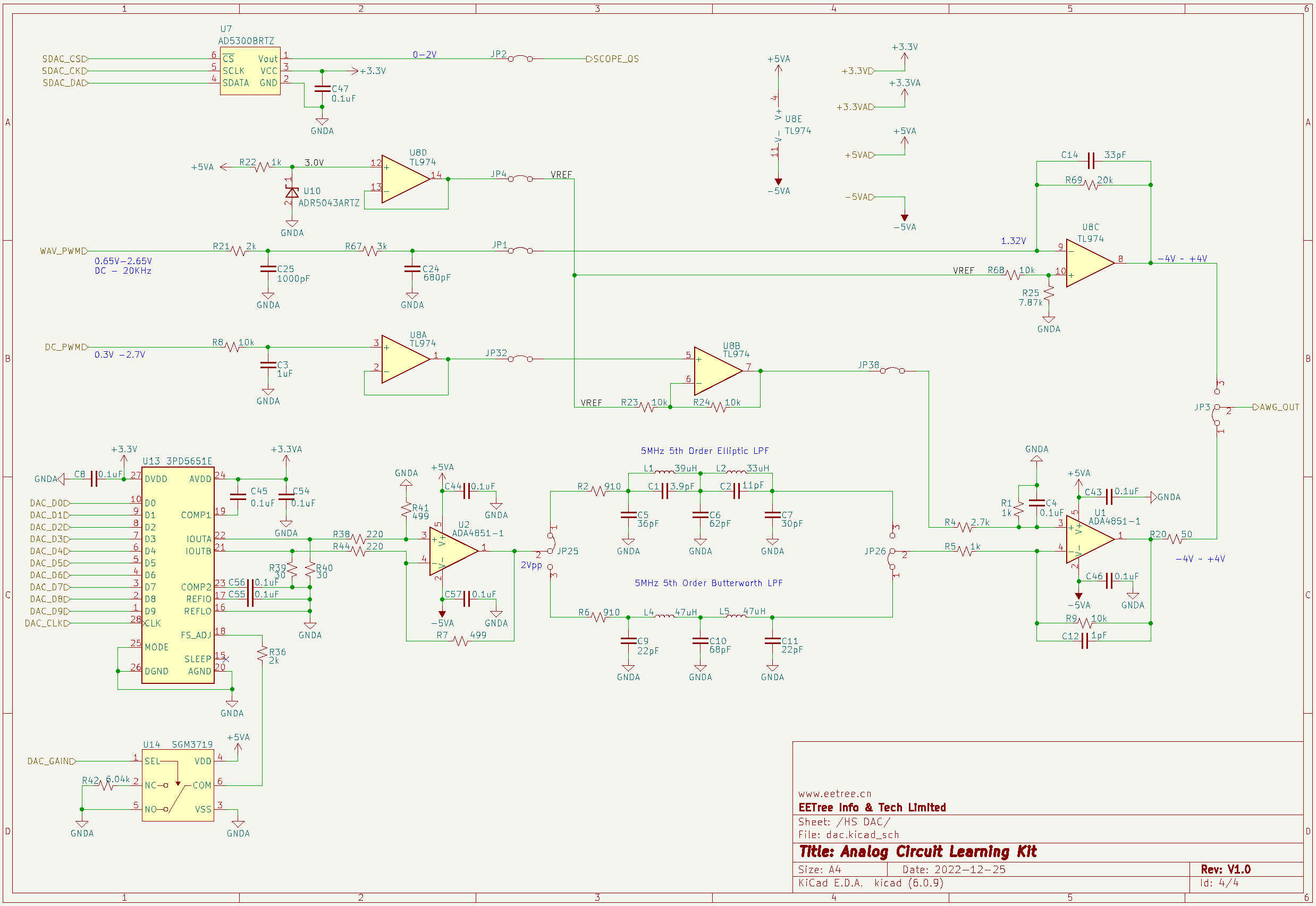

2.2 原理图

2.3 3D效果图

3 电路详解

为方便理解电路的功能构成,原理图部分划分了3个不同的功能模块,每个功能模块采用一个单页的原理图来设计,三个功能模块在顶层连接在一起。

在这个顶层页面中有3个连接器,一个为信号输出射频连接器、一个为模拟信号输入的射频连接器,还有一个是4PIn的输入/输出连接器,使用杜邦线连接,方便ADALM2000口袋仪器进行测量。 四个定位/安装孔用于安装亚克力保护板,安装在板卡底部的四个螺丝柱能够保护板卡在台面上不受台面上其它器件的干扰。

下面我们逐个功能看看一下。先看一下电源供电部分。

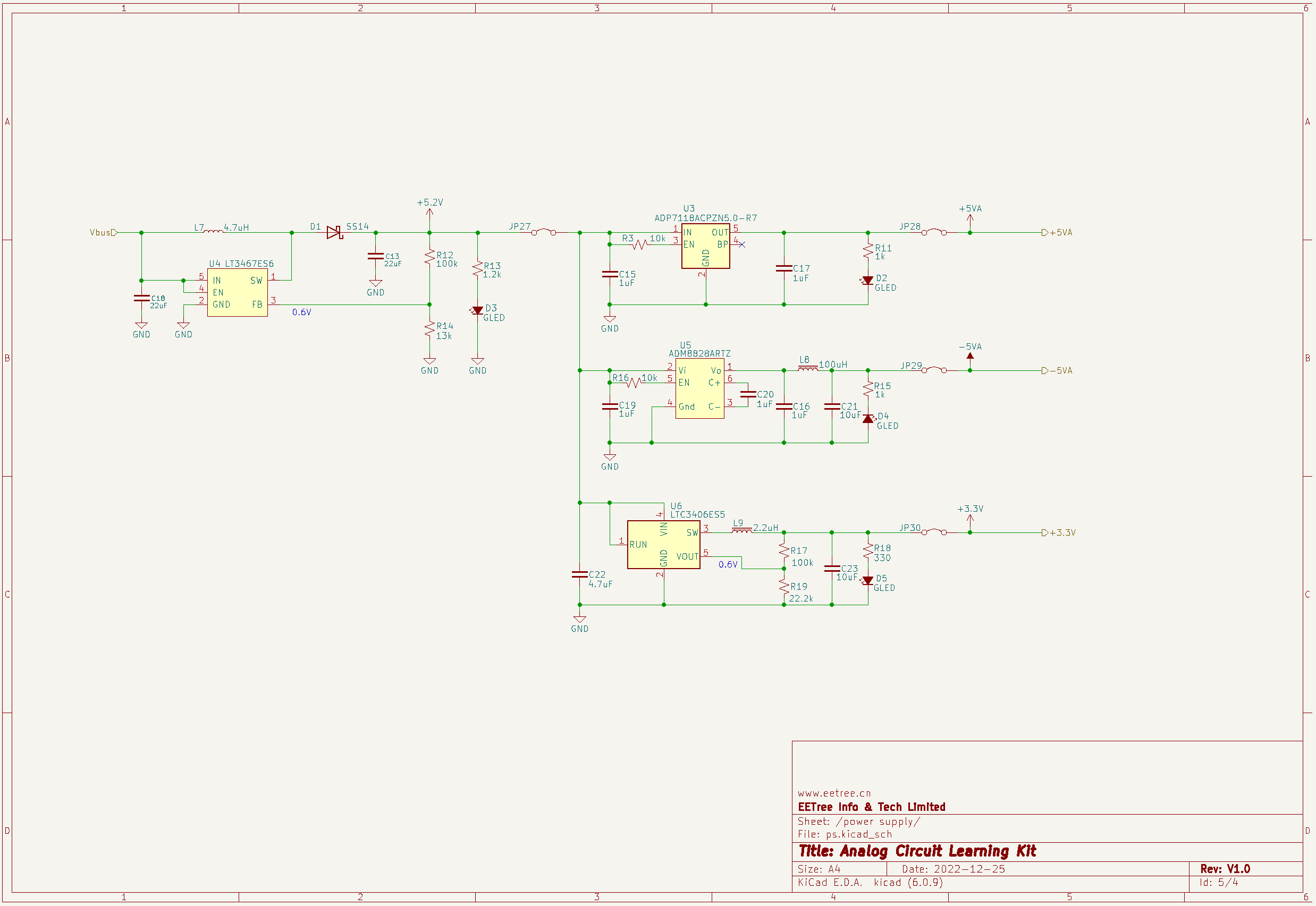

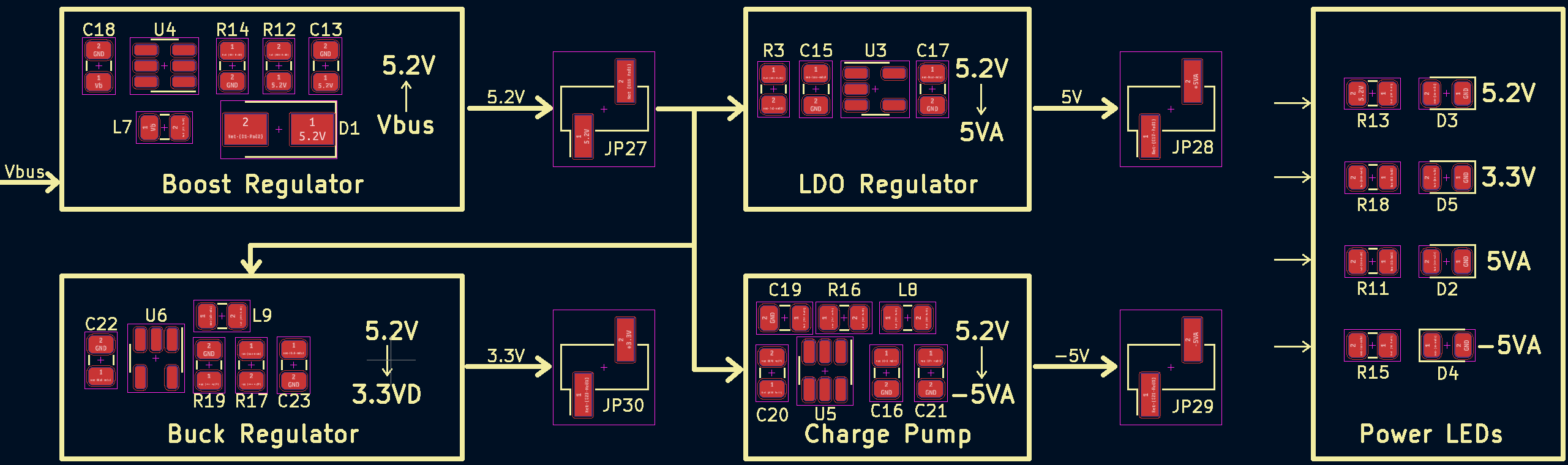

3.1 供电部分

本套件供电是通过核心板上的USB连接电脑获得5V的直流电压,考虑到USB线的阻抗导致的压降(与板上所需的功耗有关),到达电路板上的直流电压会低于5V,有时会低至4.7V,为保证模拟电路需要的5V、-5V电压,需要先通过升压电路将通过USB送到板上的直流电压进行升压/稳压,得到5.2V(在300mA负载电流下超过使用的LDO需要的最低压差,一般为100mV)的稳定直流电压,再通过LDO和电荷泵电路得到运算放大器需要的+/-5V

下面是原理图中与电源相关的部分。

电源部分的PCB布局图

电源部分的PCB布局布线3D效果图

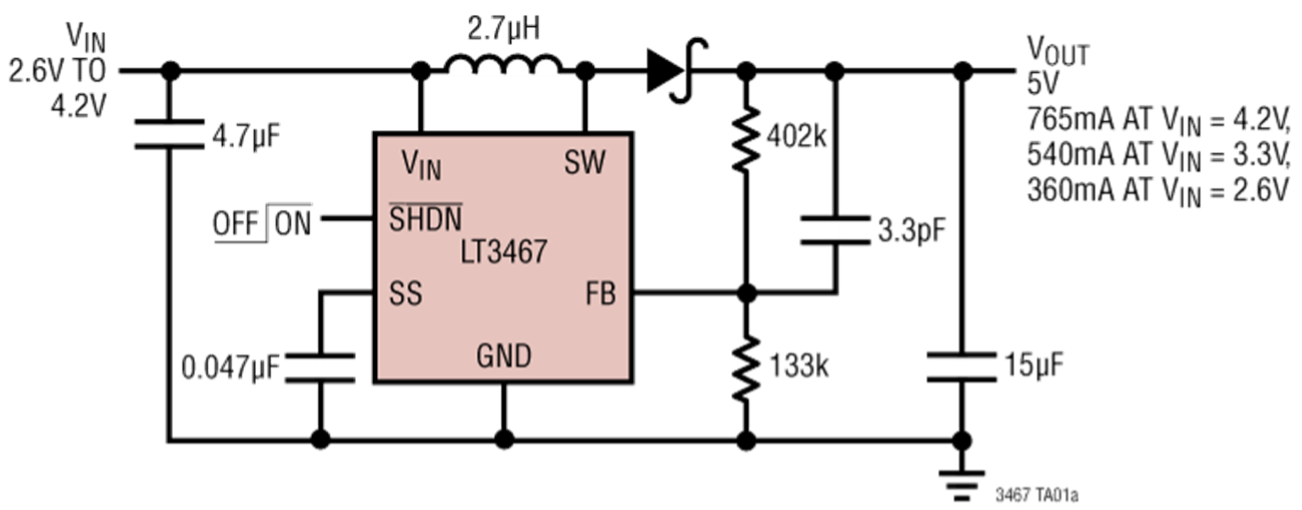

3.1.1 USB输入电压转5.2V - 开关升压电路

从USB的输入电压得到高于输入电压的直流稳定电压,采用的电源变化拓扑为开关升压电路,也被称为Boost电路的开关稳压电路。USB端口的电压一般为5V DC,考虑到USB线的压降,我们可以设定为4.7V到5V之间。后面的电路需要得到线性稳压的5V和-5V,都应该从这个开关升压后的直流电压上获取,考虑到5V的LDO需要的压降,以及电荷泵,考虑到LD和电荷泵工作需要的电压值,以及LDO的变换效率,5.2V是个比较合适的电压值,因此我设定开关升压电路的工作条件为:

- 输入电压:4.7V-5V

- 输出电压:5.2V

- 输入、输出电流:300mA

有很多开关升压器件可以来使用,为方便未来的产品化,要尽可能选择功能及管脚兼容的器件,比如我们可以选用:

- 或使用时代民芯公司的MT3608 - 高性能1.2MHz、2A升压转换器:

- 集成了80mΩ功率MOSFET

- 输入电压范围:2V到24V

- 1.2MHz固定开关频率

- 内部4A开关电流限制

- 可调输出电压

- 内部补偿

- 最高到28V输出电压

- 自动脉冲频率调制

- 6-Pin SOT23-6封装

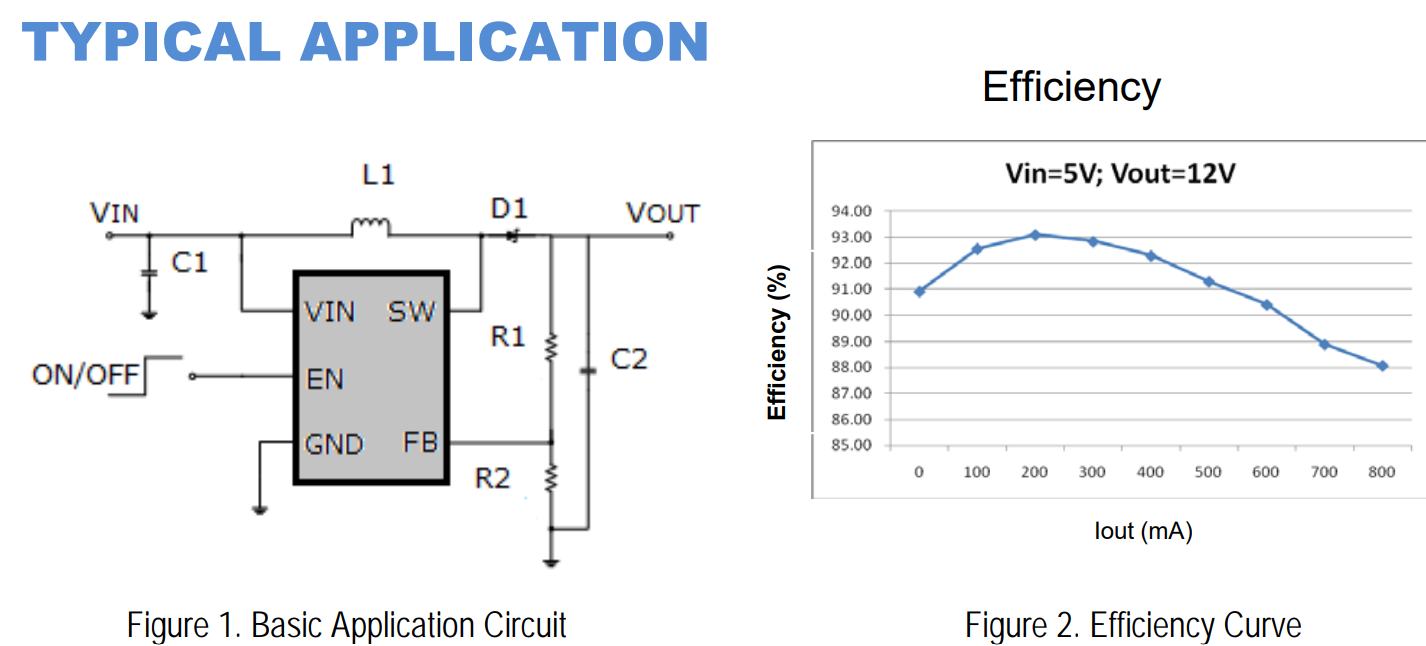

MT3608应用框图及效率

这两款器件管脚兼容,都是SOT23-6封装,它们的管脚定义也是一致的,因此可以互换。 这两款器件支持的输出电流都能够达到1A以上(LT3467支持最大1.2A、MT3608能够支持到最高2A的电流)。

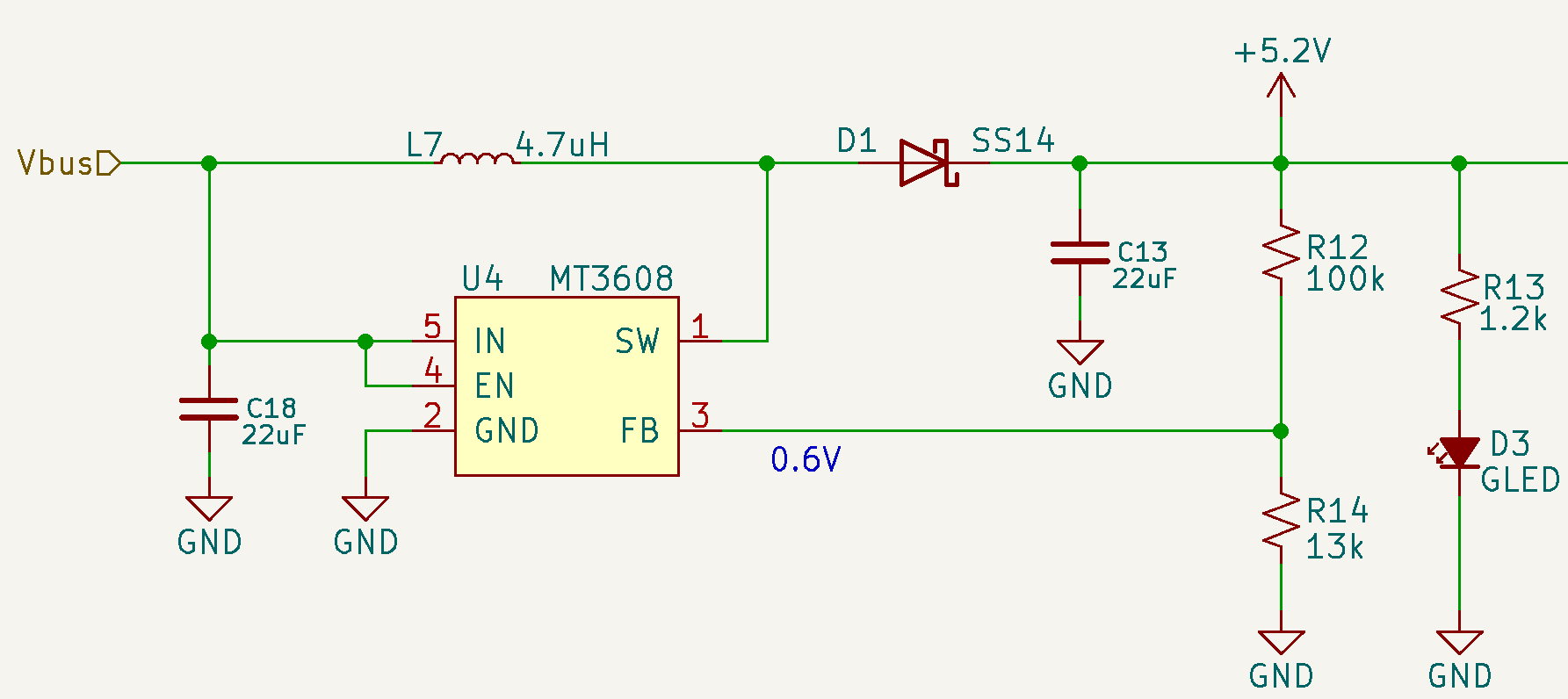

下面以MT3608来看一下如何通过开关升压电路,从4.7V到5V的直流电压得到5.2V的稳定电压。

MT3608的反馈管脚的基准电压为0.6V,如果要得到5.2V的输出电压,R12:R14 = (5.2-0.6):0.6 = 23:3

取R12为100KΩ,则R14为13KΩ

使用MT3608由USB电压产生5.2V直流电压

3.1.2 5.2V转5V LDO - 线性稳压/LDO电路

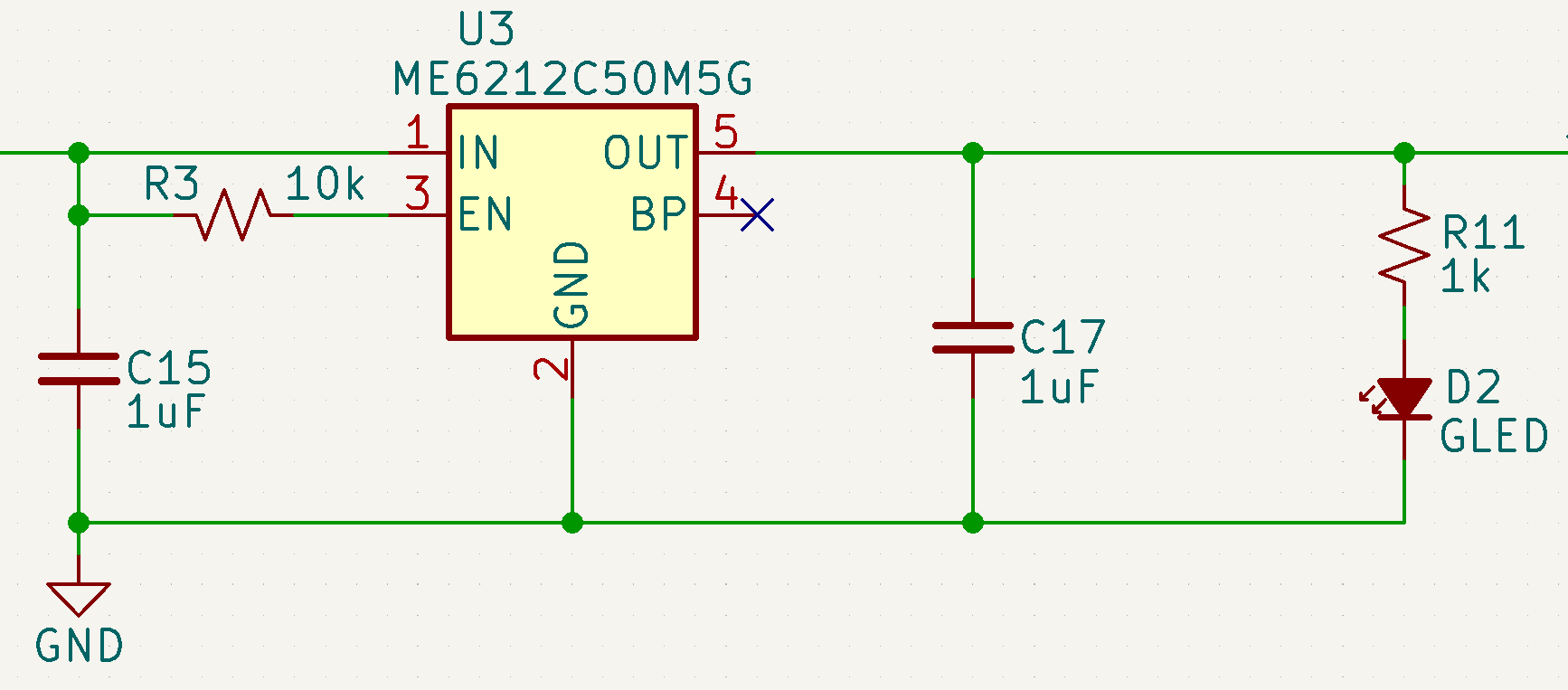

有了5.2V的稳定直流,可以通过低压差稳压器LDO来得到5V直流电压,供给板上的模拟器件,比如模拟开关、模拟运算放大器等。板上需要5V供电的器件并不多,100mA的电流就已经足够。

LDO有固定电压输出,也有可调电压输出,为简化电路,可以直接采用输出固定电压(比如5.0V)的LDO。

同样我们在元器件选型的时候尽可能选用功能一致、管脚完全兼容的器件,比如:

-

- 输入电压范围: 2V到6V

- 固定输出1.2V到5.0V,间隔0.1V

- 输出电流350mA

- 低压差: 120mV (TYP) at 100mA

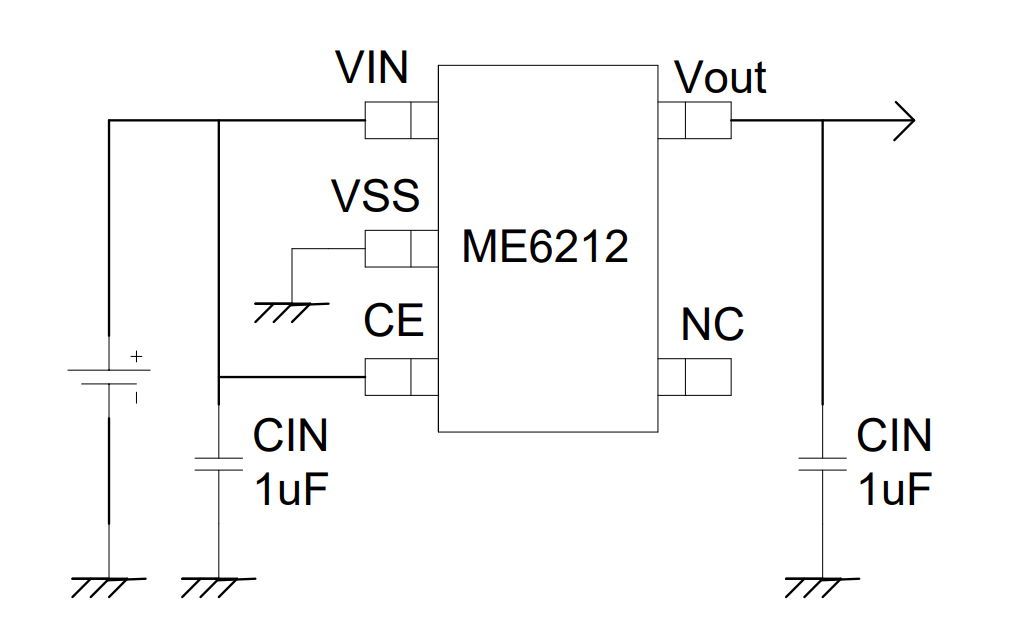

ME6212的应用框图

使用ME6212由5.2V得到5V直流电压

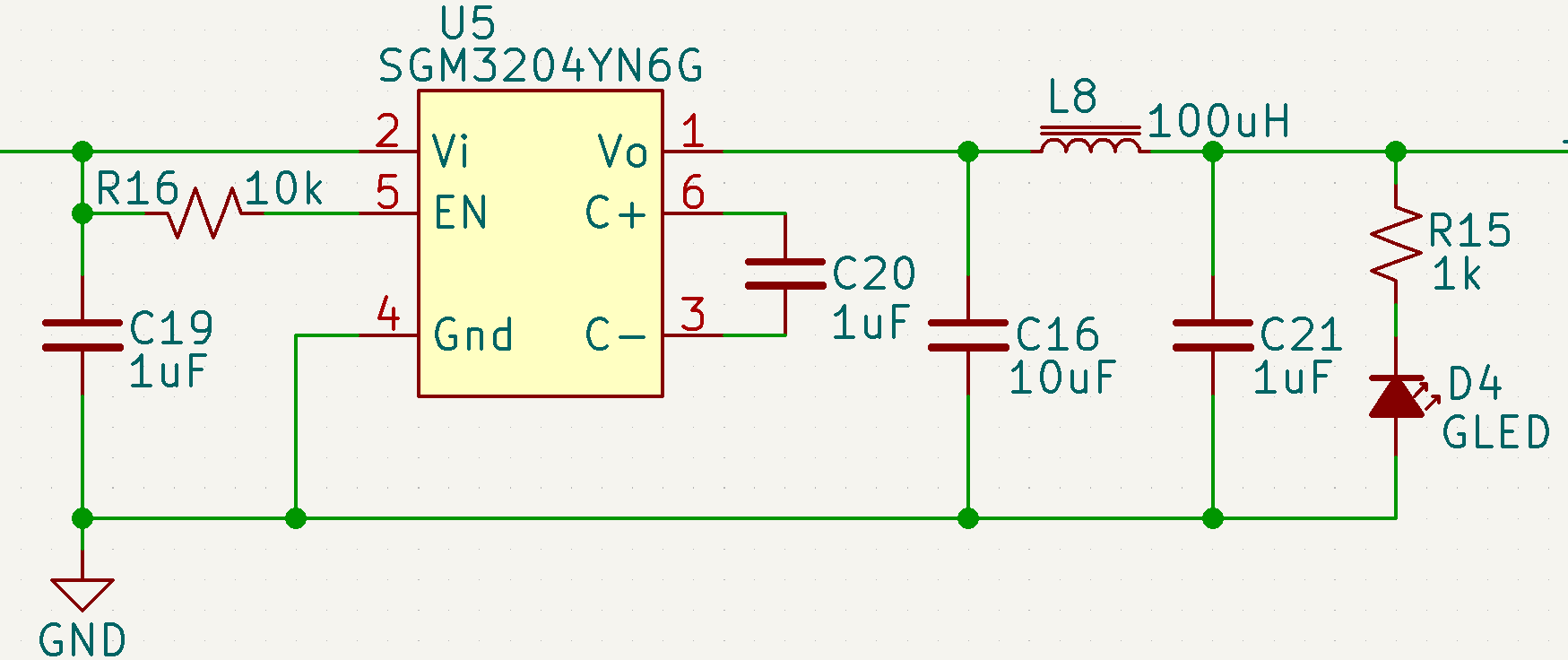

3.1.3 5.2V转-5V电荷泵

模拟电路比如运放、模拟开关等一般都需要+/-双轨电压,最简单的由正电压得到负电压的方式就是通过电荷泵,也叫开关电容变换器,它是通过电容储能的方式来实现,相对于采用电感储能的开关变换方式,产生的纹波电压较低。

通过电荷泵方式可以从+5V得到-5V,在100mA左右负载电流的情况下压降在200mV左右,也就是说能够从+5V得到-4.8V,从+5.2V得到-5V的直流电压。

同样,我们也使用管脚兼容的电荷泵器件,比如:

这两颗芯片管脚完全兼容,功能相同,可以替代。

使用SGM3204电荷泵芯片由5.2V得到-5V直流电压

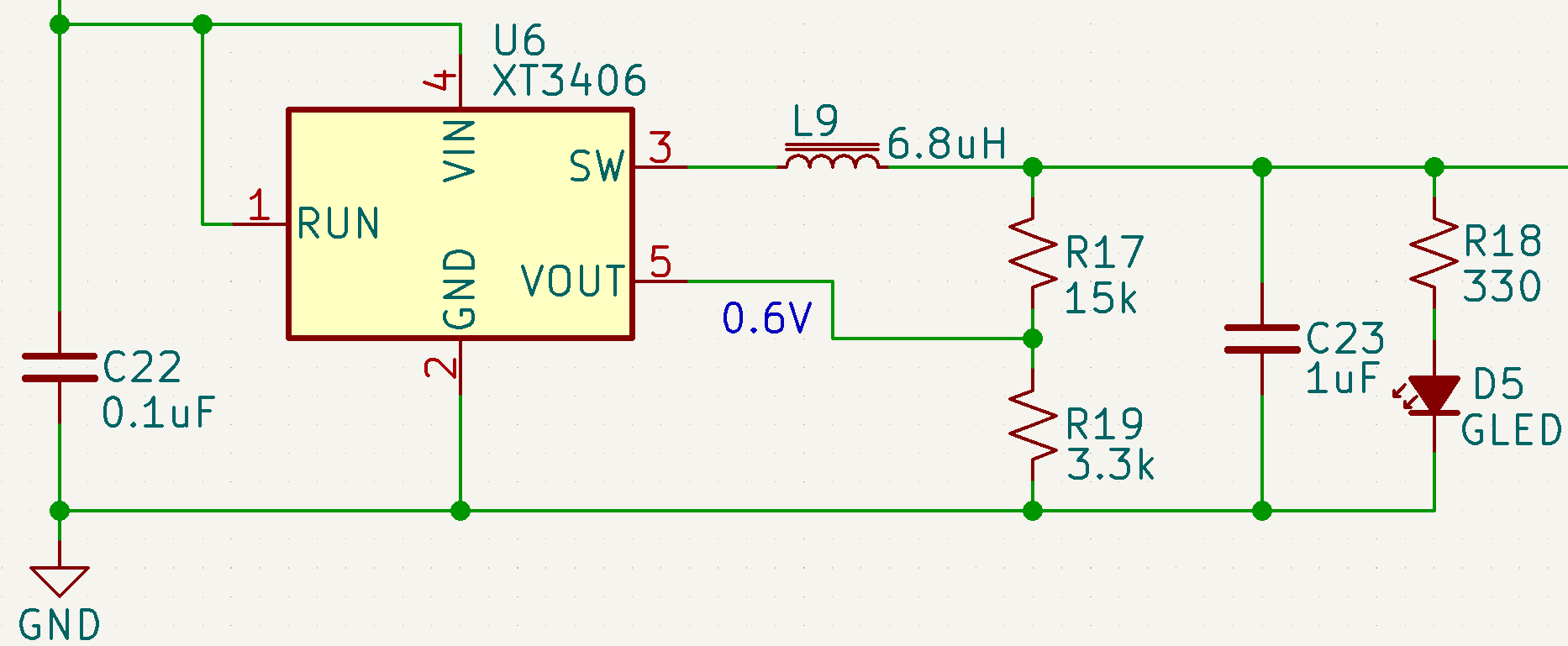

3.1.4 5.2V转3.3V 开关降压

R17:R19 = (3.3-0.6):0.6 = 9:2

取R17为100kΩ,则R19=22.2kΩ,选择常规值22KΩ,实际得到的输出电压为3.327V

使用XT3406由5.2V得到3.3V直流电压

3.2 信号发生电路

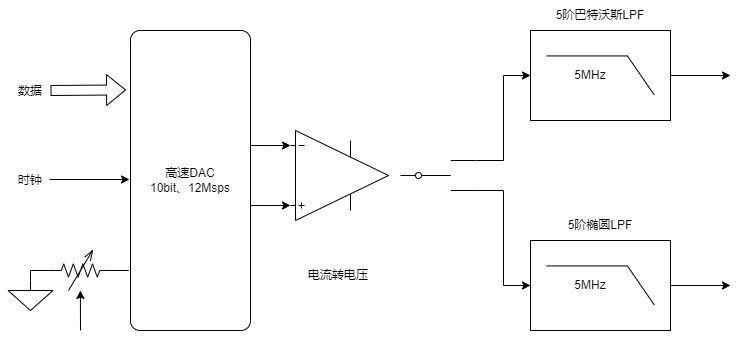

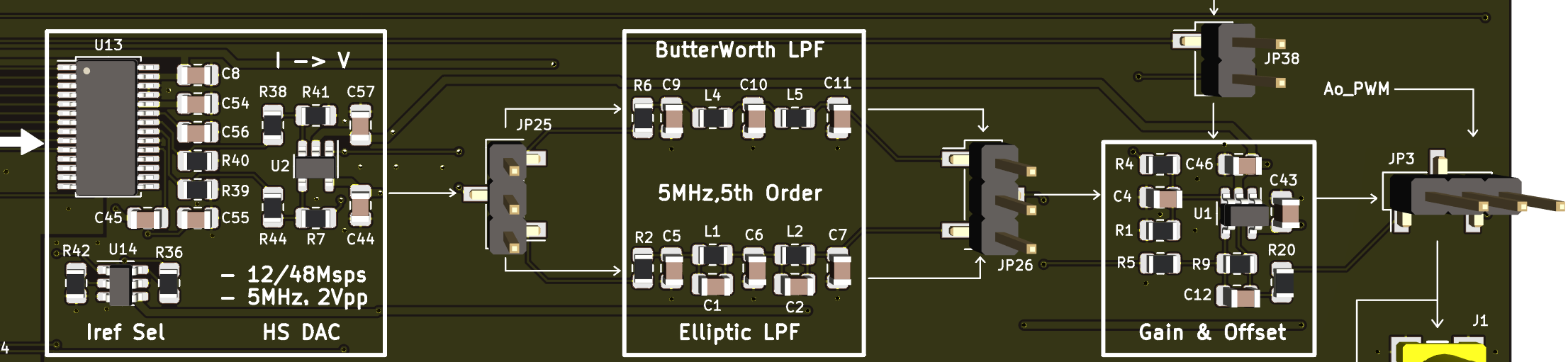

3.2.1 高速DAC + 差分电流转单端电压

电路中采用了3Peaks公司的10位精度、最高转换率达125Msps的高速DAC - 3PD5651,在本设计中我们同时支持WebIDE编译环境(FPGA的内部时钟只能到12MHz)、Lattice或Altera的官方编译工具(通过PLL内部逻辑能够工作到200MHz)以及ICE40 FPGA的Radiant,ICE40 FPGA最高只能运行在48MHz,因此我们DAC的转换率最大设定为48Msps、生成的模拟信号的带宽为5MHz,后续的滤波器电路也是按照5MHz来设计。

关于3PD5651E:

- 125MSPS转换率

- 10-Bit分辨率

- 线性度: 1/4 LSB DNL

- 线性度: 1/2 LSB INL

- 差分输出电流: 2mA到20mA

- 到40MHz奈奎斯特输出的SFDR: 62 dBc

- 快速建立时间: 35ns满量程设置到0.1%

- 片内1.10V基准电压

- 边沿触发锁存

- 功耗: 175 mW @ 5 V to 45 mW @ 3 V

- 休眠模式: 20 mW @ 5 V

- 单+5V或+3V供电

- 28脚TSSOP封装

我们通过一个模拟开关SGM3719来切换为3PD5651E提供基准电流的外置电阻,分别为2K和8K,在这两种配置下,DAC的满量程输出为:

- 2KΩ:1.1V/2K * 32 = 17.6mA

- 8KΩ: 1.1V/8K * 32 = 4.4mA

这两种配置,满足3PD5651最大满量程为2mA到20mA之间的要求,不会带来系统失真。

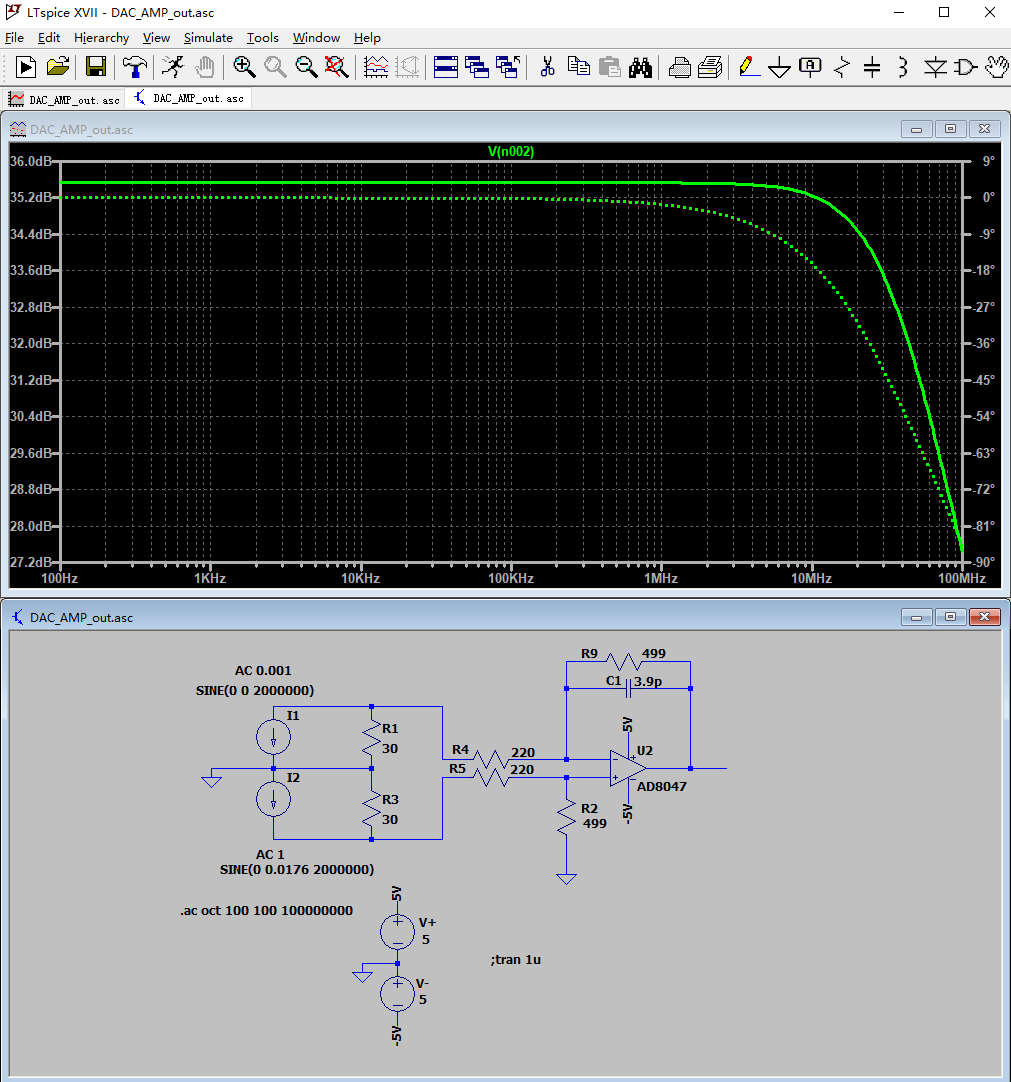

DAC后面接了一个差分电流转单端电压输出的电路,在使用两种不同电阻配置的情况下,对应的最大电压信号输出:

- 2KΩ:1.1V/2K * 32 * 30 * 2 * 2 = 2.112Vpp

- 8KΩ: 1.1V/8K * 32 * 30 * 2 * 2 = 0.528Vpp

高速DAC输出电压的波形仿真

高速DAC输出电压的频谱响应

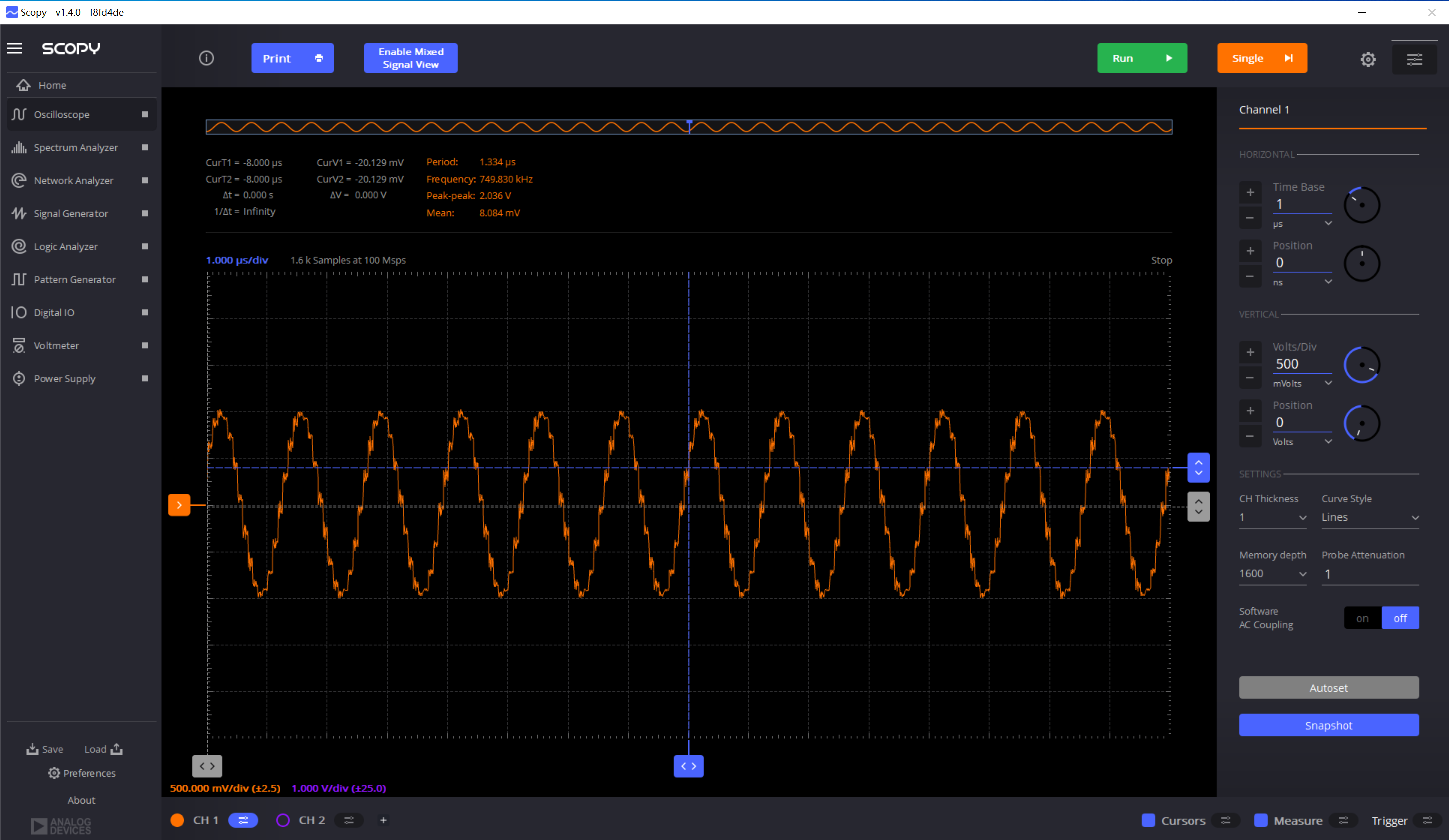

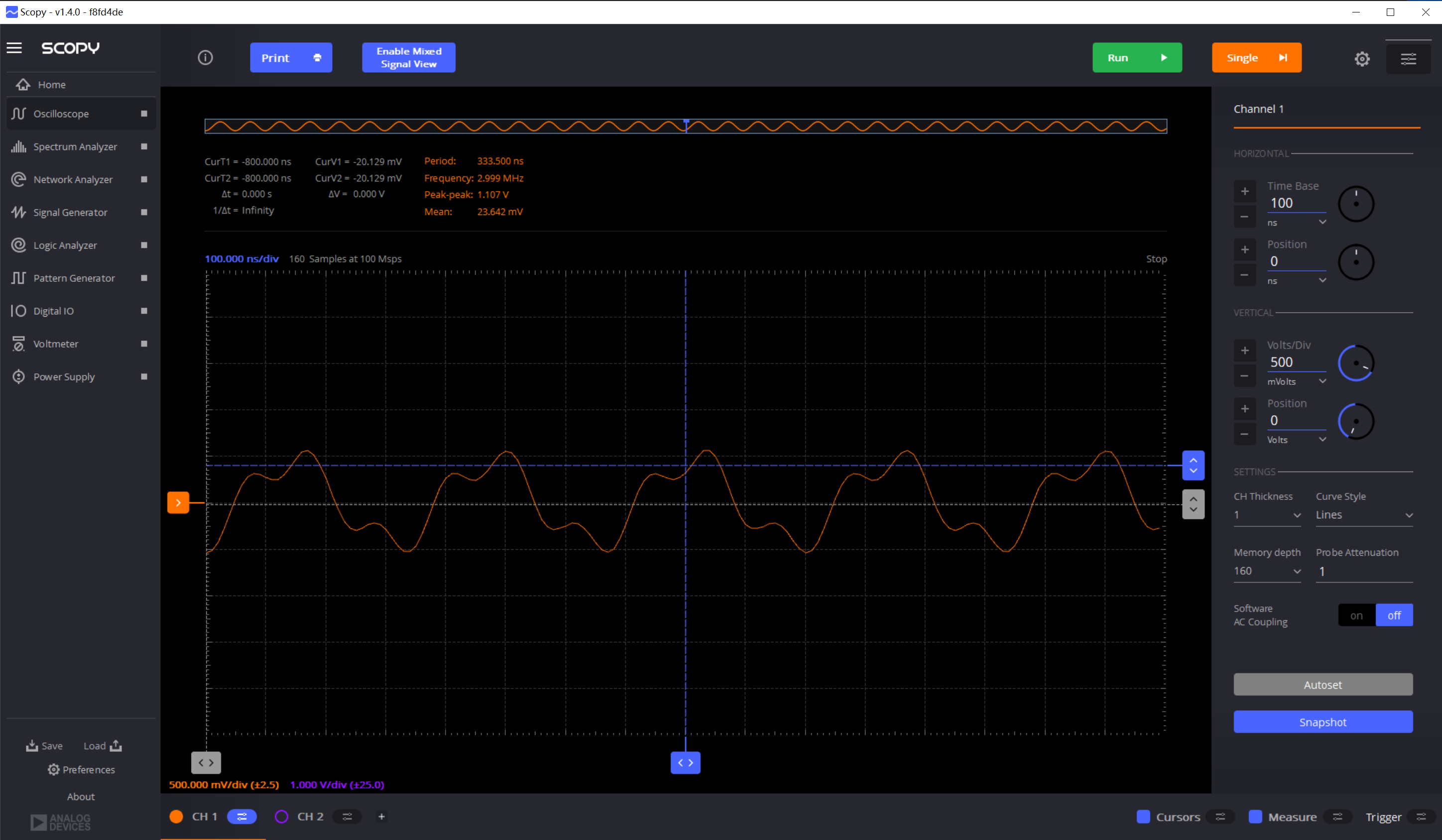

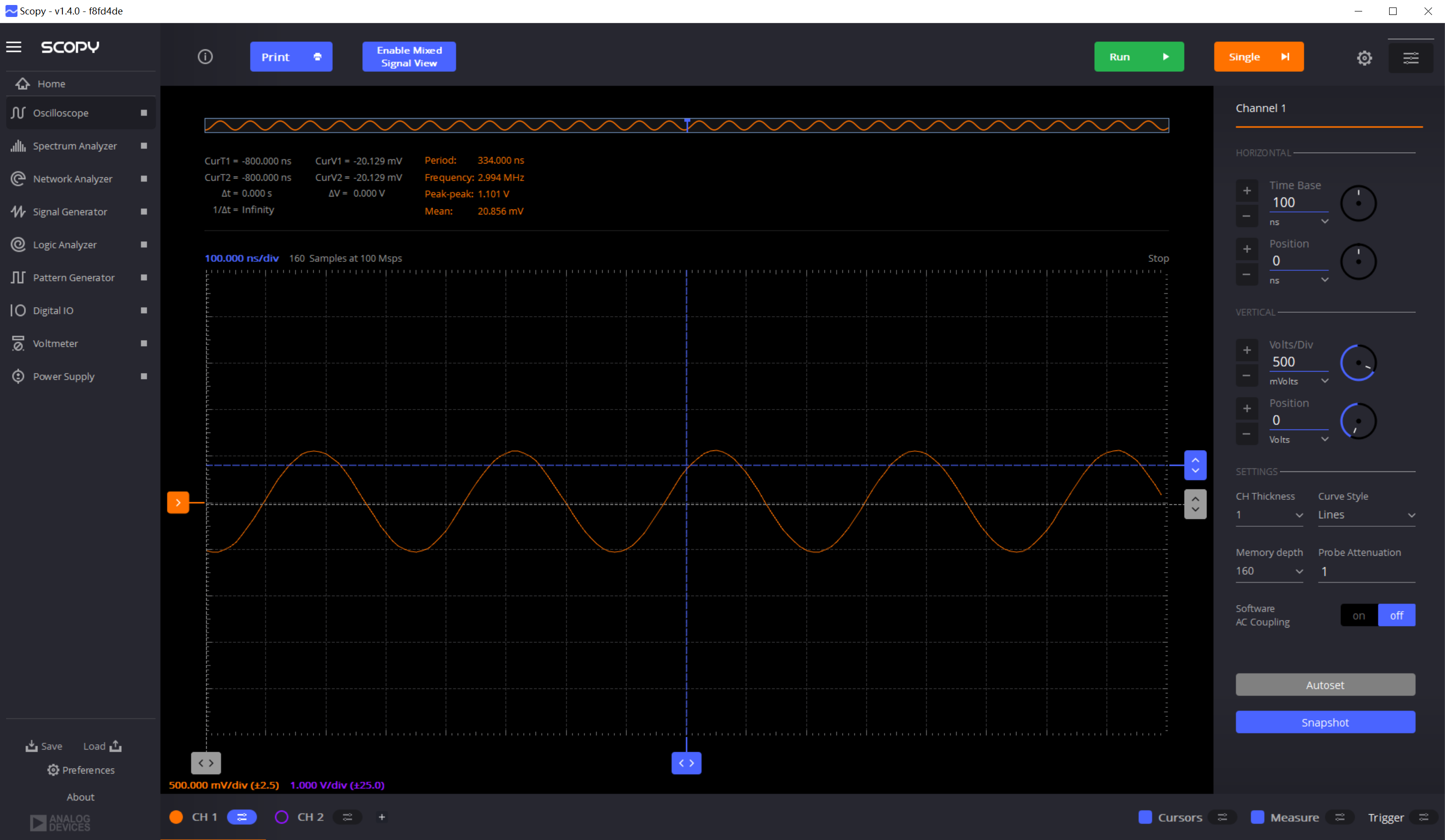

高速DAC输出3MHz正弦波信号的波形,12Msps转换率

高速DAC输出750KHz正弦波信号的波形,12Msps转换率

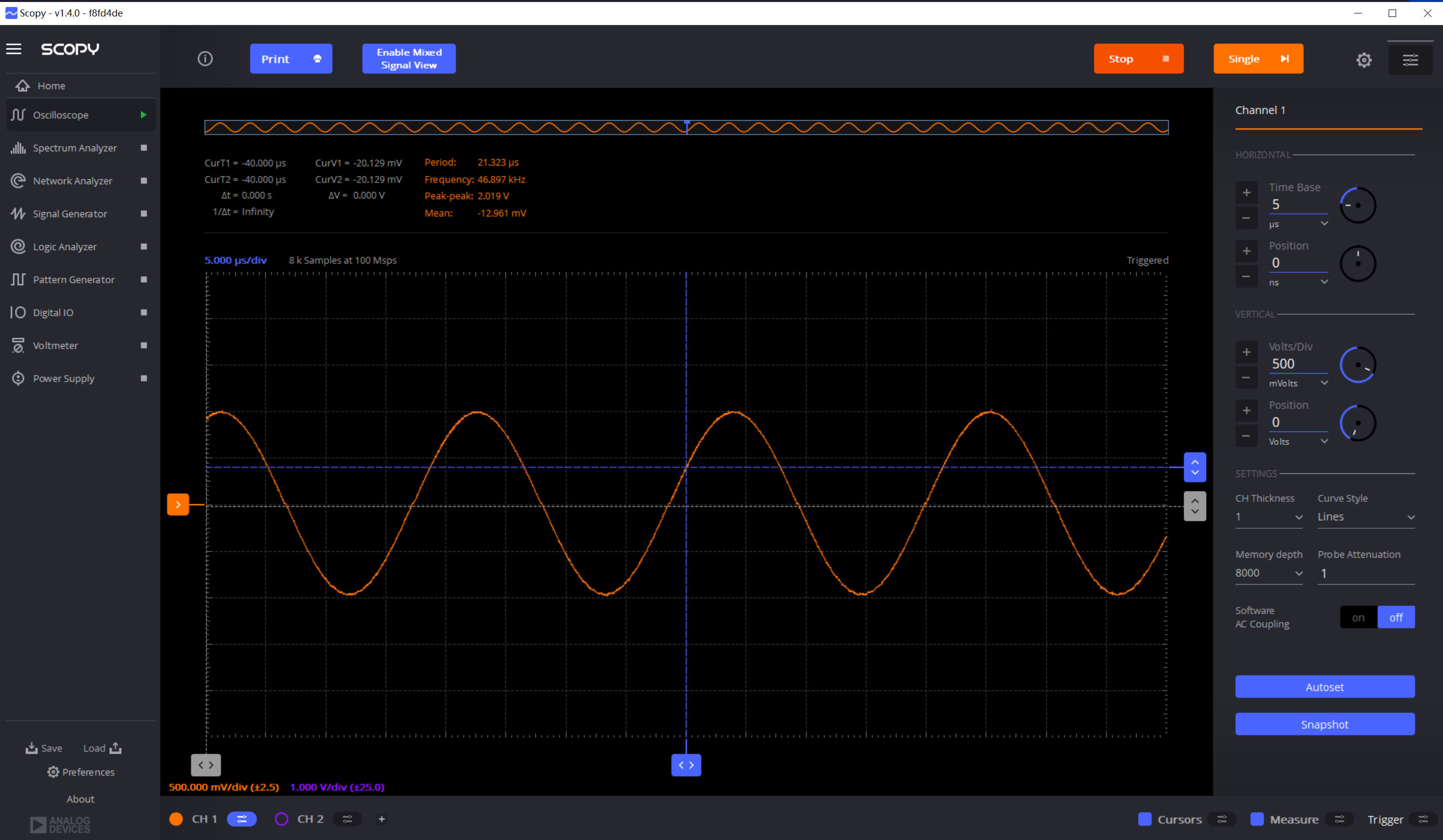

高速DAC输出46.875KHz正弦波信号的波形,12Msps转换率

高速DAC输出46.875KHz正弦波时的频谱

3.2.2 5阶低通滤波器

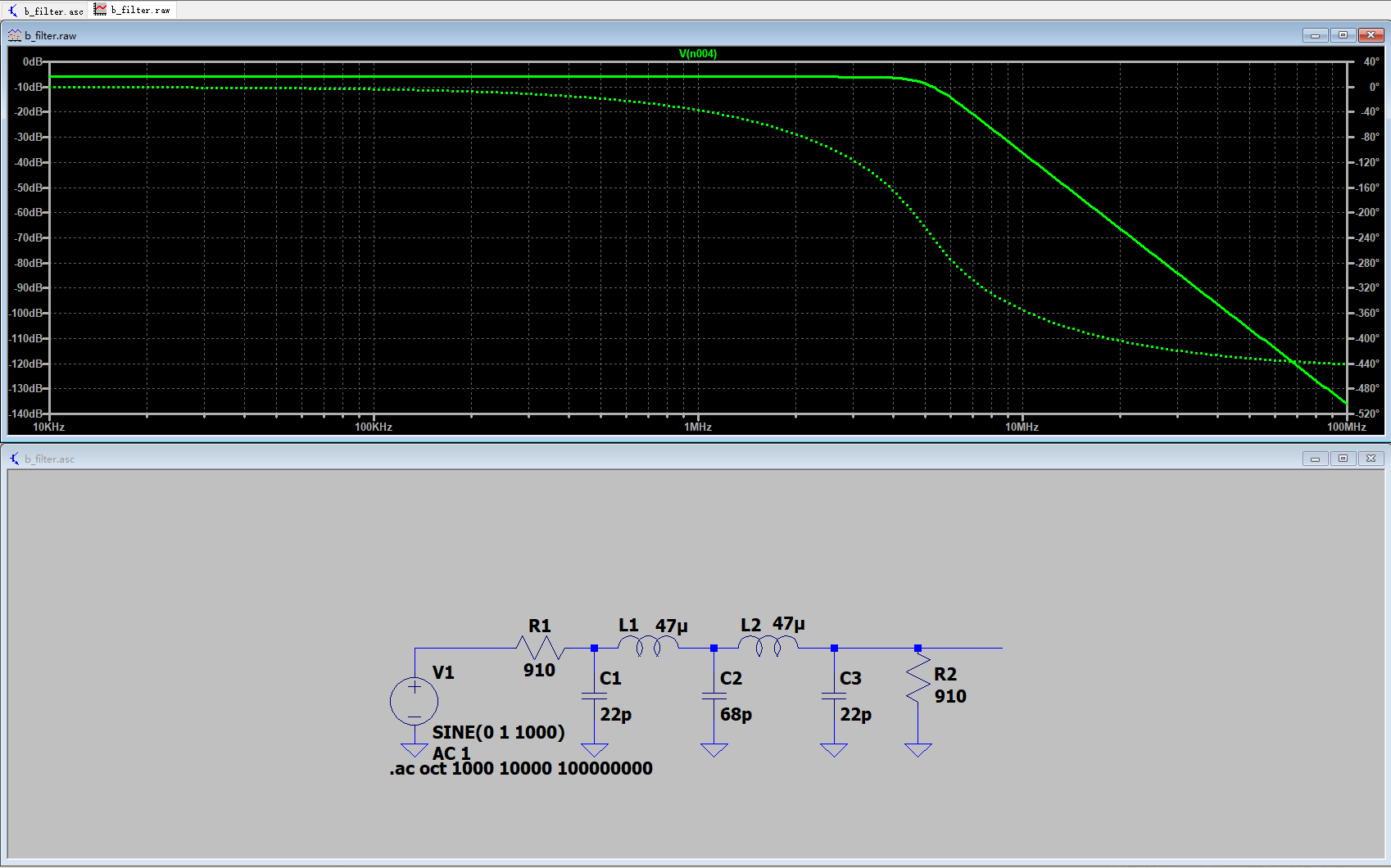

5阶巴特沃斯滤波器的频率响应

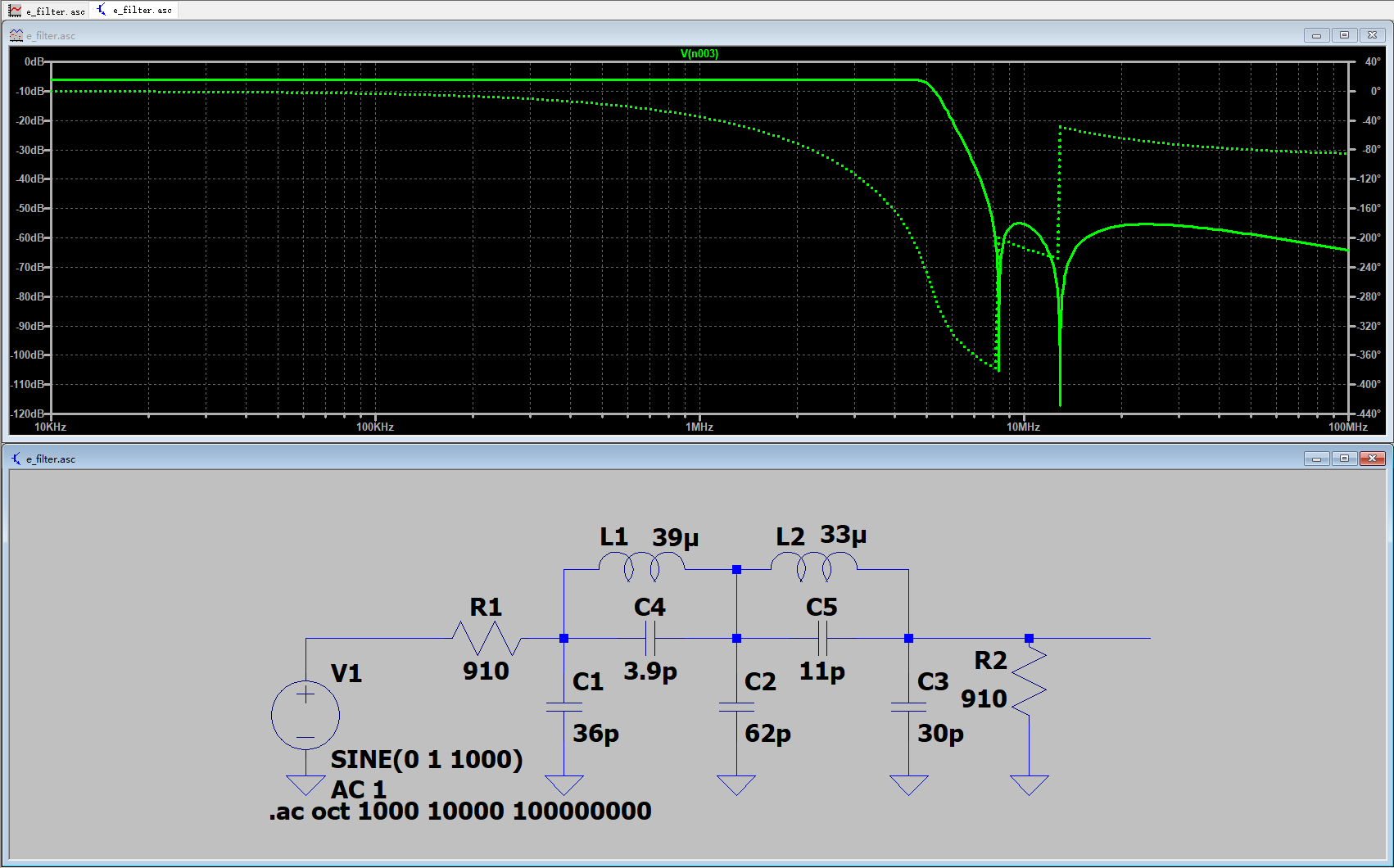

5阶椭圆滤波器的频率相应

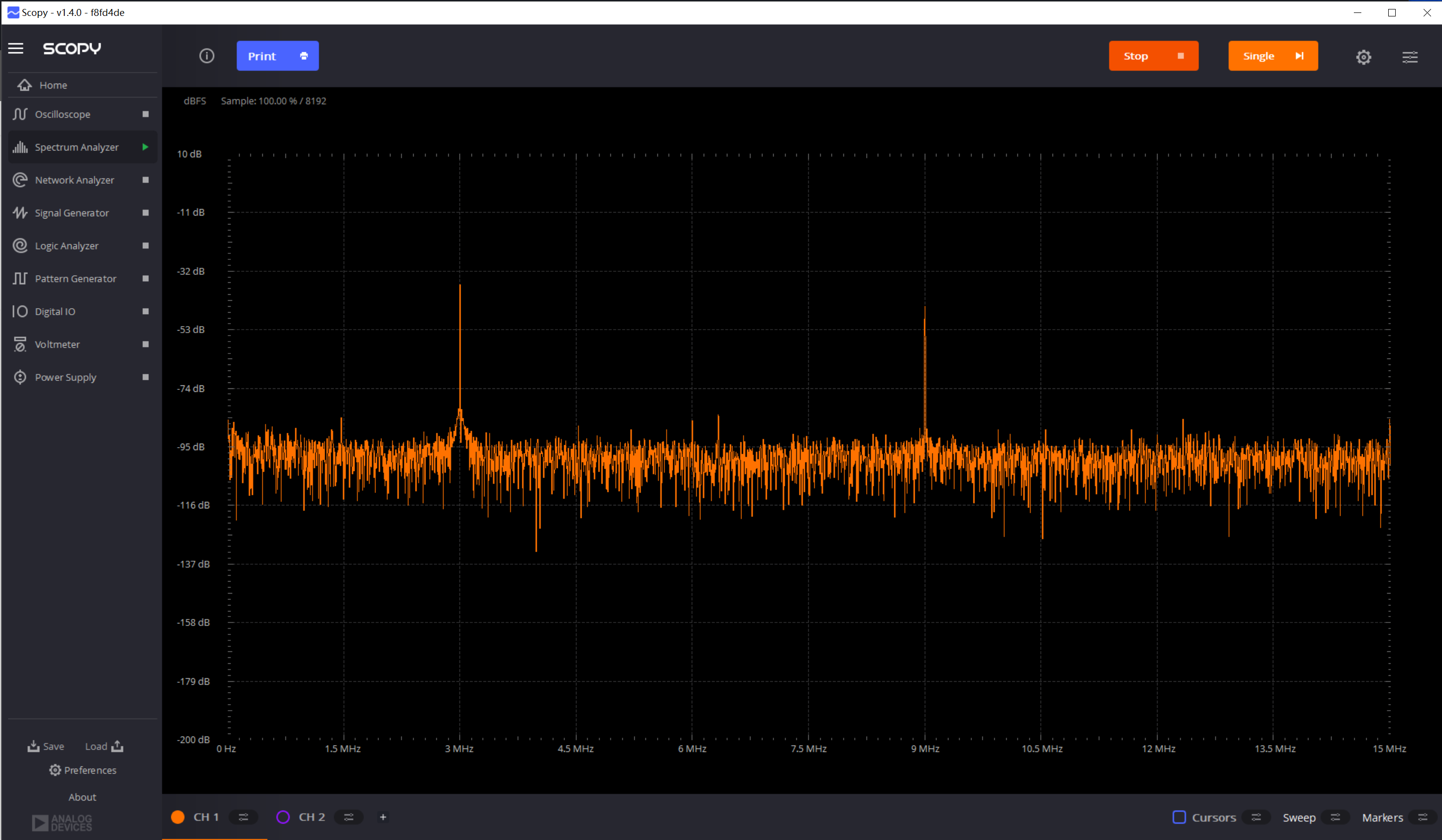

3MHz的信号通过5阶巴特沃斯滤波器后的频谱

3MHz的信号通过5阶椭圆滤波器后的频谱

3MHz的信号通过5阶巴特沃斯滤波器后波形

3MHz的信号通过5阶椭圆滤波器后波形

750KHz的信号通过5阶巴特沃斯滤波器后波形

750KHz的信号通过5阶椭圆滤波器后波形

3.3 信号采集电路

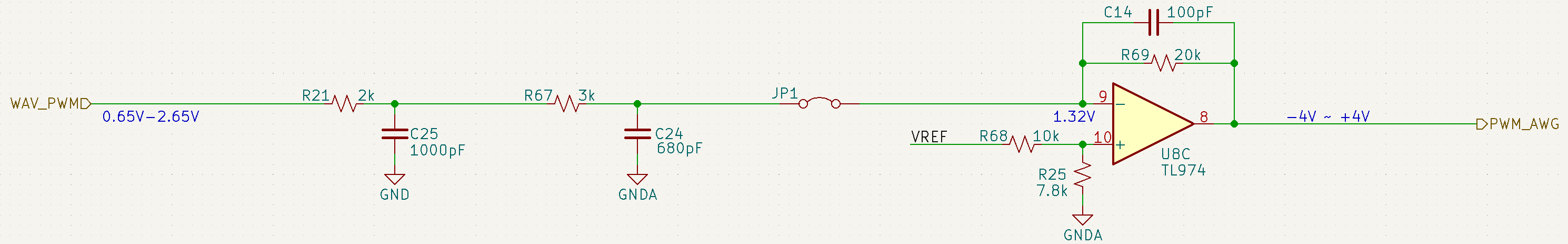

3.4 通过PWM产生模拟信号

我们可以使用pwm来实现DAC的效果,pwm本质上是使用低频信号来调制数字脉冲的占空比,用于调制的低频信号可以是直流电压,也可以是任意波形,比如信号发生器中常用的正弦波、方波、三角波等。对pwm信号“解调”,就可以恢复出调制在脉冲宽度上的低频信号。调制的功能是在数字域实现,解调的过程是通过低通滤波器来实现。 因此,可以通过在数字域用数字的方式将低频的信号波形(以波表的形式)来生成不同脉宽的脉冲信号,再通过低通滤波器对其进行解调,就可以得到在数字用波表构建的低频信号波形。

只需要一根数字信号线和一个电阻、电容构成的低通滤波器就可以实现DAC的功能,这个“等效DAC”的转换率和分辨率取决于生成PWM的主时钟频率(决定了脉冲的最小宽度)和调整载波的重复频率。

在本套件上,我们通过2阶RC构成的低通滤波器+由运放构成的1阶有源滤波器网络将PWM信号恢复要生成的低频率的模拟信号,再通过运算放大器扩大信号的输出幅度。我们设定LPF的截止频率为音频信号的上限20KHz,并在输出端增加一个耳机插座,可以生成音频信号,通过耳机来听用数字逻辑生成的音频信号。

PWM为数字信号,数字信号的最高幅度为3.3V(小脚丫FPGA的数字IO供电为3.3V),为实现更好的解调效果,PWM采用Delta Sigma的方式,这种方式的特点是占空比越接近50%,输出信号的高频分量越远离低频调制信号,如果我们控制PWM的占空比在20%-80%之间,就非常容易实现相对较高的上线频率而且低通滤波器的设计也会比较简单。

因此,我们解调信号的幅度度控制在以1.65V为中心的2Vpp - 0.65V到2.65V,对应的占空比为0.65V÷3.3V = 19.7%到2.65V÷3.3V = 80.3%

由于板上运算放大器的供电为最高+5V和-5V,即便使用了Rail-to-Rail的运算放大器,当输出信号的幅度峰峰值超过9Vpp的时候,也会失真,因此我们设定输出信号的最大幅度为8Vpp,也即输出的模拟信号在-4V到+4V之间。

运算放大器的增益就就设定为8Vpp ÷ 2Vpp = 4,因此取运算放大器的输入阻抗R21+R67为5KΩ,反馈电阻R69为20KΩ

将1.65V的中心电压通过运算放大器变换为以0V为中心的电压,需要在运放的输入端进行偏置,可使用基准电压生成的3.0V来通过分压电阻R68和R25来实现.

(1.65-Vamp-)/(R21+R67) = Vamp-/R69

考虑到R69÷(R21+R67) = 8Vpp/2Vpp =4

得到:Vamp-=1.65V * 4/5 = 1.32V

Vamp+ = Vref * (R68+R25)/R25 = Vamp-

得到:R68 ÷ R25 = 1.2727,选取符合这个比例的两个标准值电阻R68=10KΩ,R25=7.8KΩ

实际在Vamp+得到的直流电压为1.315V,与理论值1.32V有0.005V的偏差(5‰),考虑到电阻本身的精度(一般为5%)这个误差在电阻精度导致的误差范围之内。

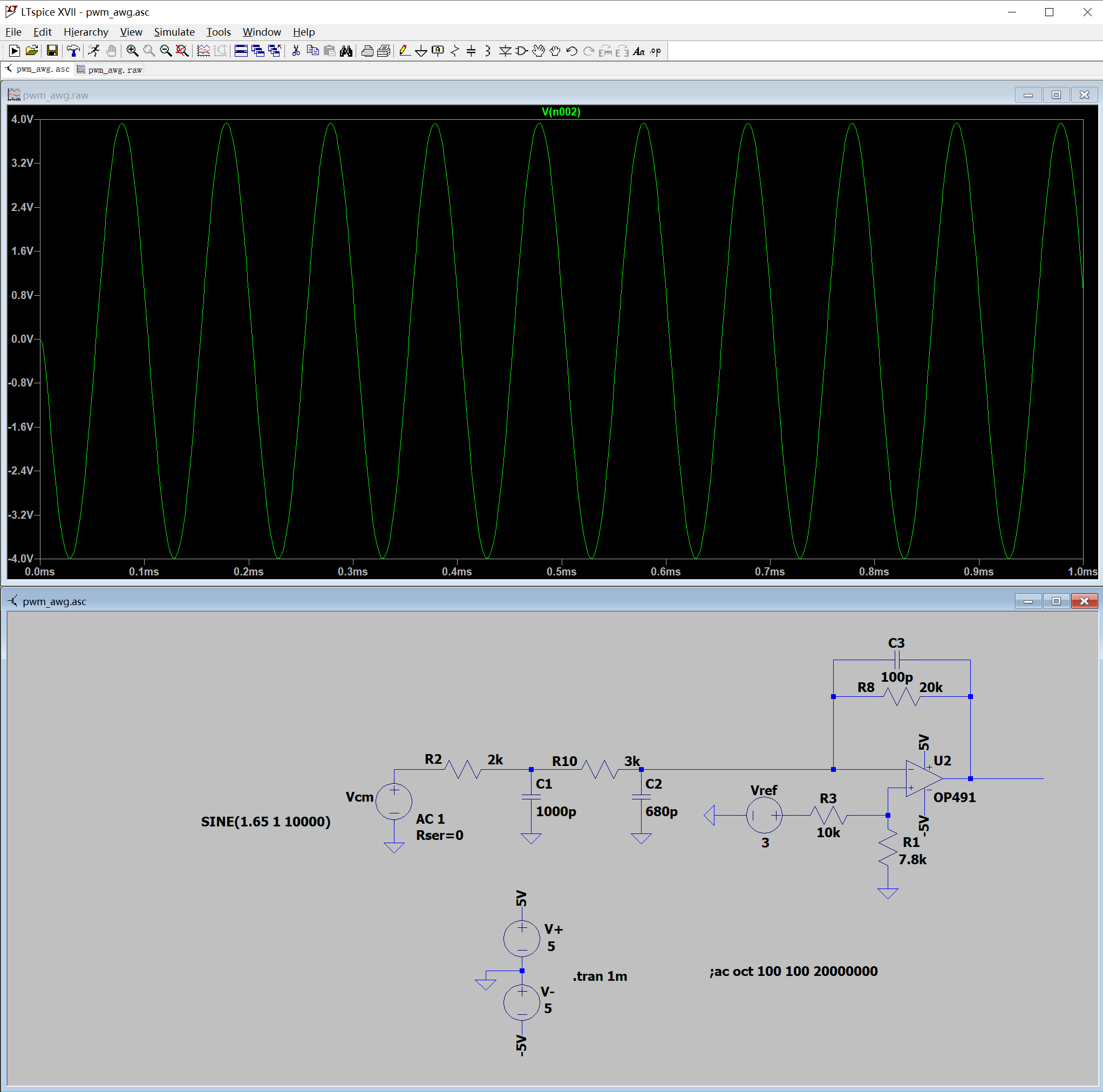

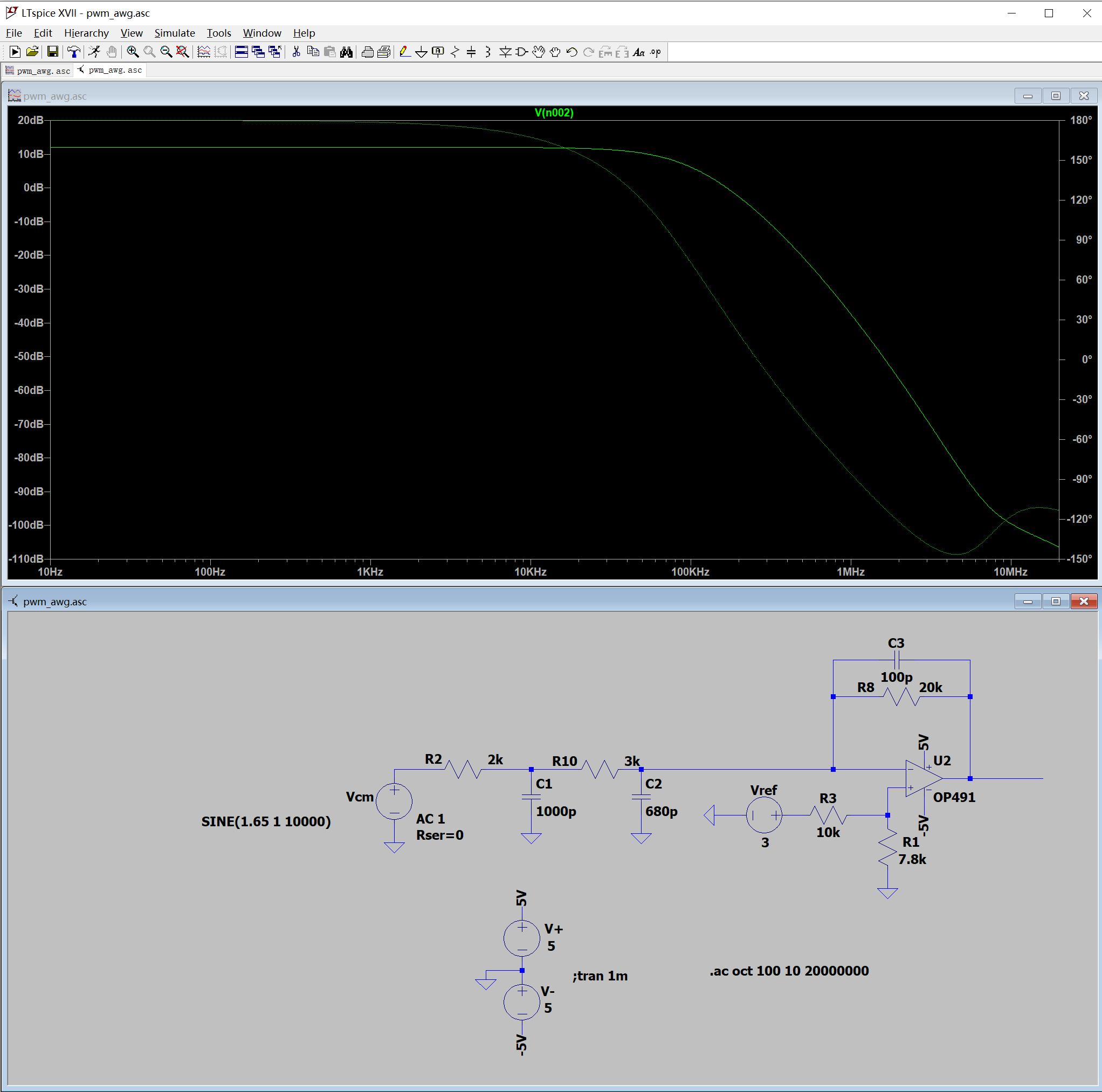

使用LTSpice仿真结果(使用ADI公司的OP491代替板上使用的TL974,二者参数接近)如下:

使用LTSpice仿真结果(使用ADI公司的OP491代替板上使用的TL974,二者参数接近)如下:

用LTSpice仿真的时域波形

用LTSpice仿真的频域效果

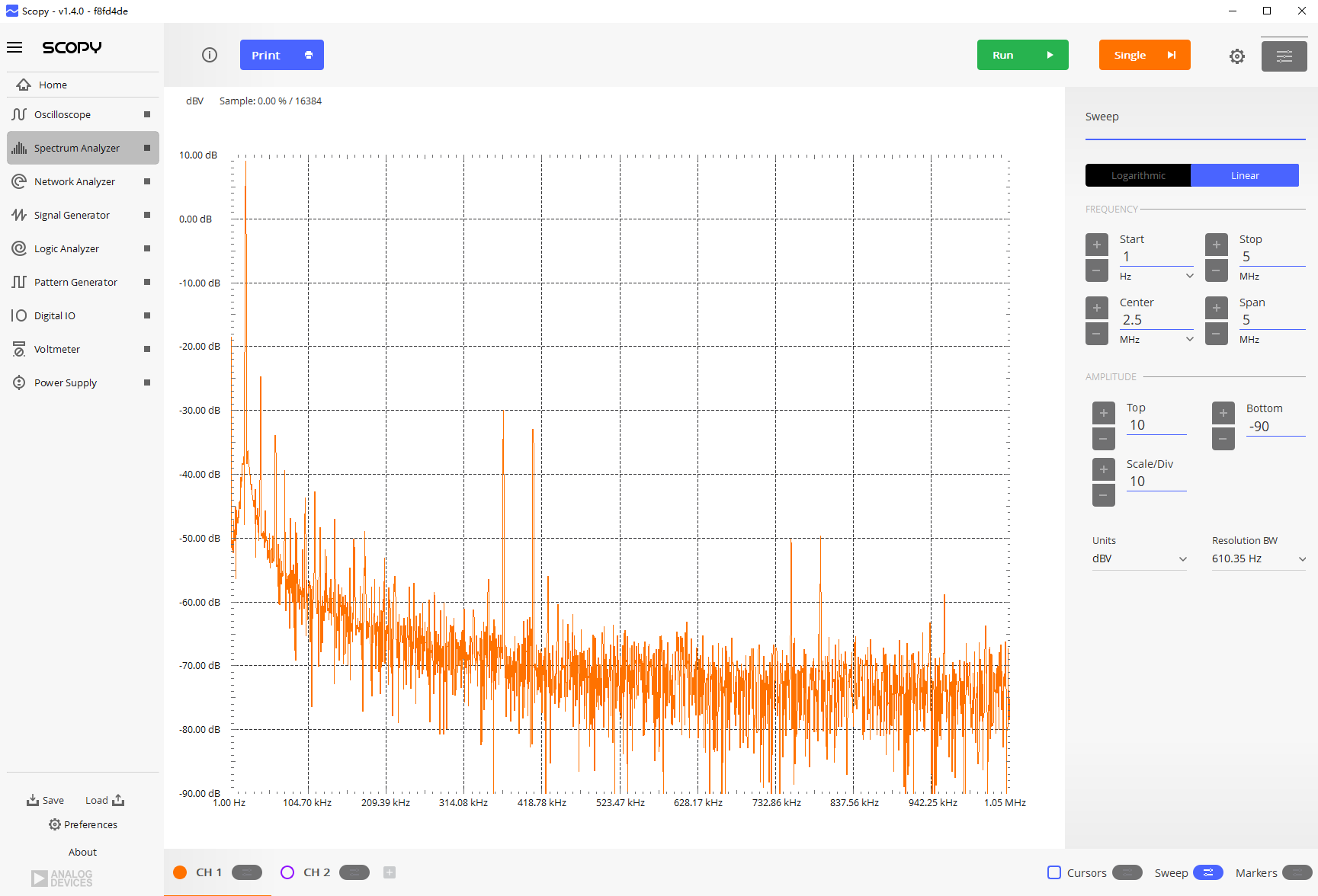

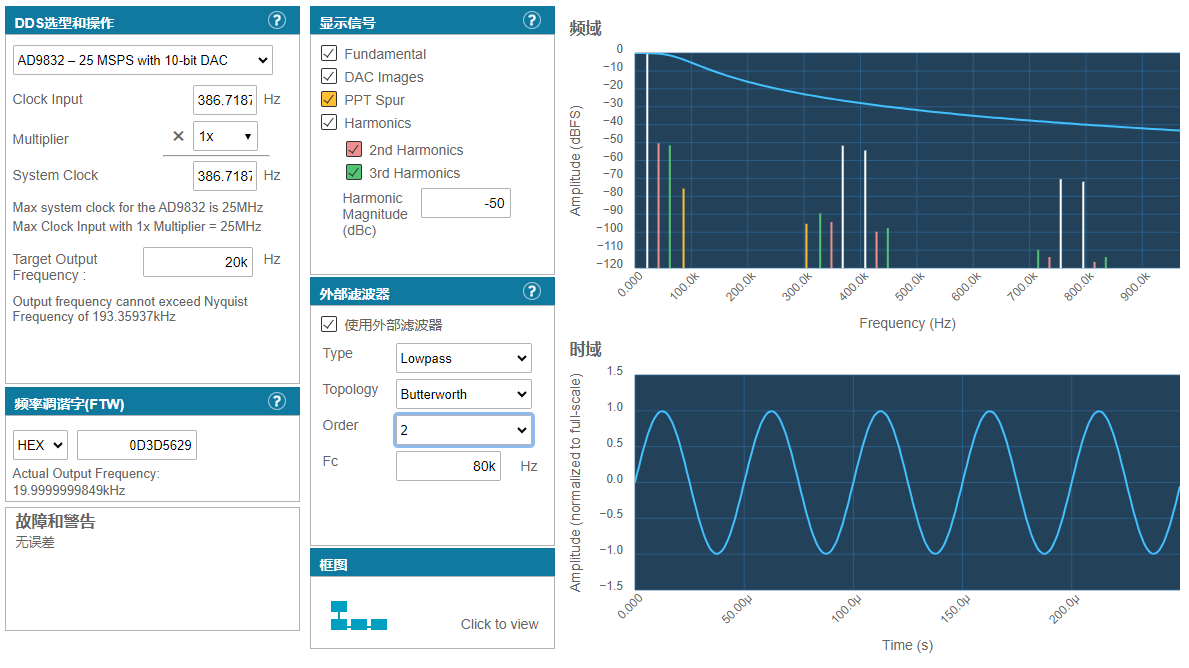

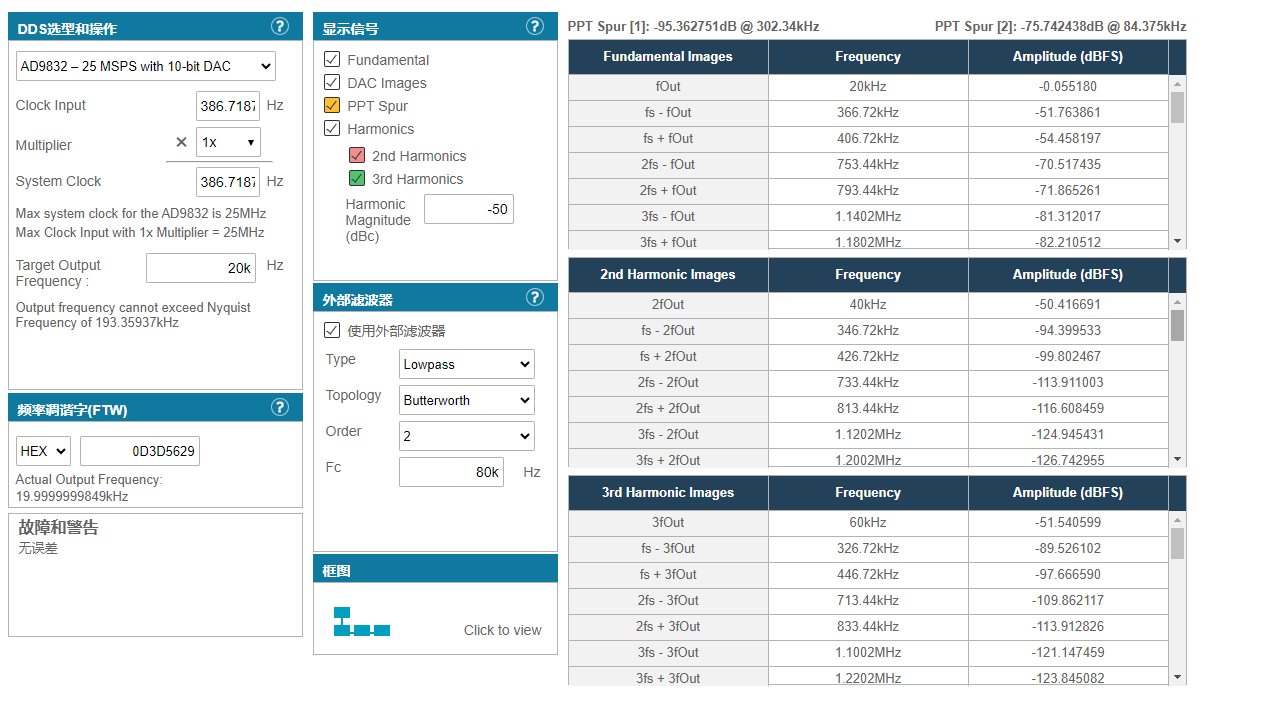

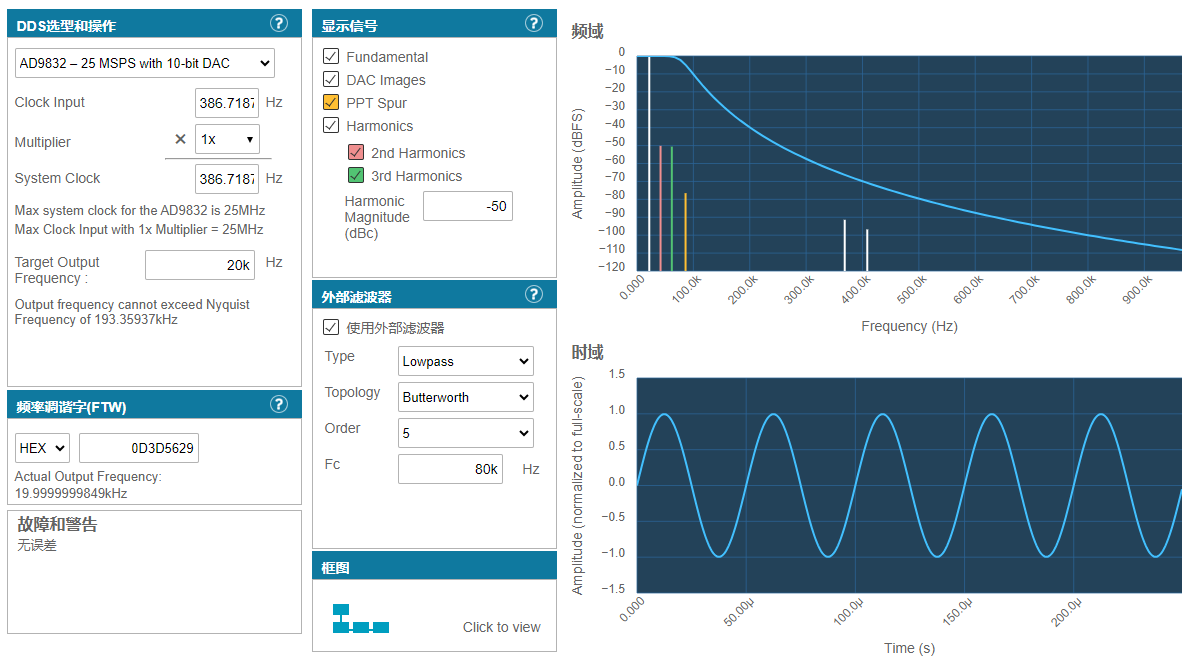

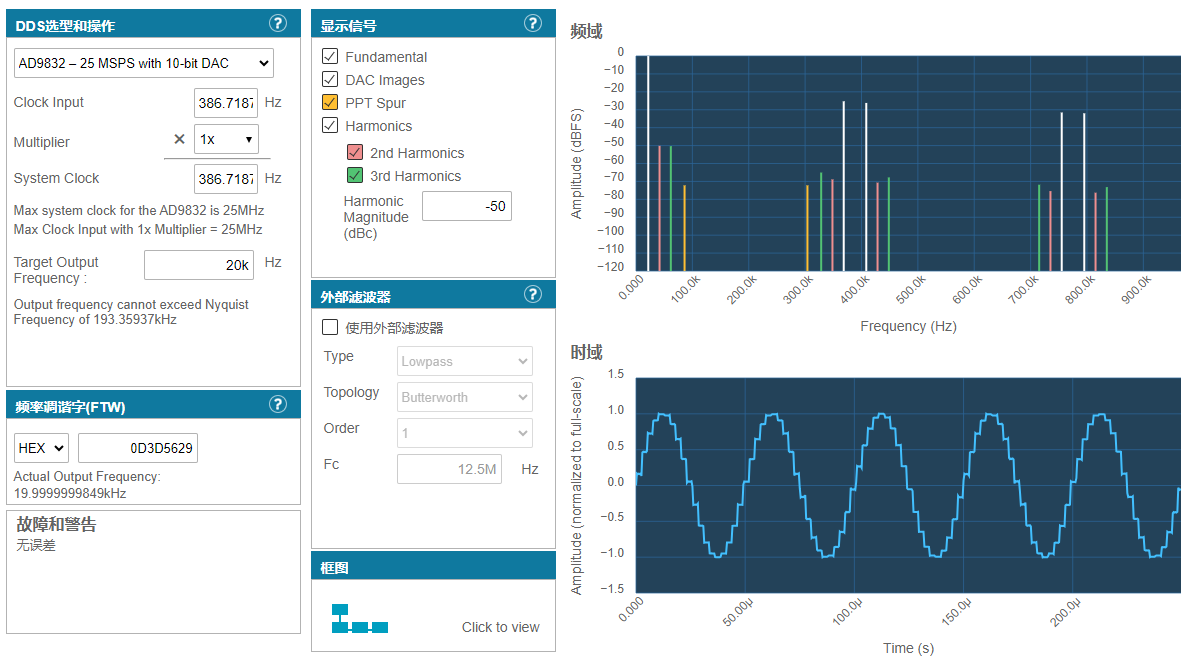

实际测试: 12MHz输入时钟,经过PLL后得到396MHz的内部时钟,用于PWM信号的生成。 AWG信号的幅度采用10位精度,因此DDS的转换时钟为396MHz/1024 ~ 386.71875Ksps 要得到20KHz的模拟信号,24位的相位累加字为24'H0D3D56

396MHz主频生成20KHz的模拟信号波形

396MHz主频生成20KHz的模拟信号频谱

在频谱上可以看到在386.71875KHz左右各有一个20KHz的镜像频率366.71875KHz和406.71875KHz的频率分量,这是因为我们低通滤波器在366KHz ~ 406MHz的抑制度比较低,如果采用更高阶的低通滤波器,可以将这部分的频率分量压制下来。

使用simDDS查看生成信号的频谱 - 没有加低通滤波器

使用simDDS查看添加了2阶低通滤波器后的频谱

使用simDDS查看添加了2阶低通滤波器后的杂散信号表

使用simDDS查看添加了5阶低通滤波器后的频谱

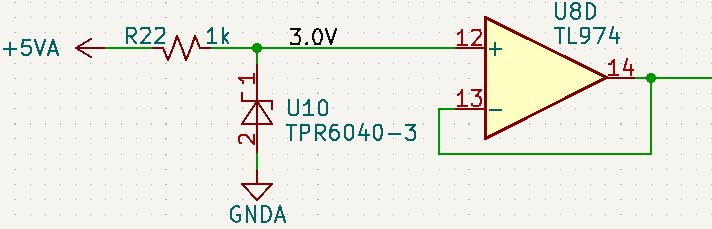

3.5 可调直流电压生成

对于信号发生器产生的信号,我们一般要求输出信号的幅度变化的同时,其信号的直流量也是可以调节的,我们可以给运算放大器的输入端添加可调节的直流电压,进而控制输出信号的直流偏移量。

在数据采集端的ADC,其接收的电压范围在0-1V之内,其中心点为0.5V,如果测试信号为0V,到ADC输入端应该是0.5V,这个直流的偏移也是通过在运算放大器的输入端加上能够调节的直流电压信号实现的。

在我们的套件上,提供了两种生成可调节直流电压的方式,一种是通过PWM信号 + LPF的方式,来给ADC的输入信号提供偏移直流量;另一种方式是使用串行DAC,通过I2C或SPI对串行DAC内部的寄存器进行设置,从而在其输出端得到想要的直流电压,提供给信号产生链路输出端的运算放大器。

PWM比较简单、几乎没有成本;串行DAC价格远超电阻、电容,且需要多根数据线来跟DAC器件通信,SPI总线需要3根信号线。

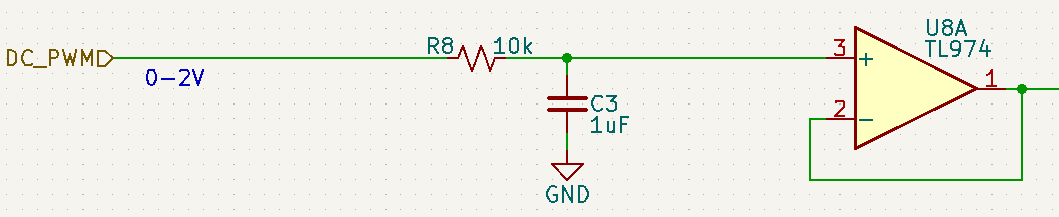

用PWM生成可以调节的直流电压,给ADC的输入信号提供直流偏移控制信号

用串行DAC生成可以调节的直流电压,给信号发生器的输出级运算放大器提供直流偏移控制信号

3.6 基准电压

3.7 Sigma Delta ADC

4. 学习的知识点

4.1 PCB设计、焊接、调试

- 学习使用KiCad设计PCB

- 设计一个扩展板,支持LCD显示、LED点阵显示、按键控制

4.2 测试测量仪器原理及使用

- 主要介绍ADALM2000的功能及使用

4.3 模拟电路设计及仿真

- 学习CircuitJS、LTSpice等仿真软件的功能和使用

4.4 FPGA的应用

- 基于小脚丫FPGA核心模块,学习基于WebIDE的Verilog编程以及FPGA的基础应用。

- 基于Diamond或Radiant来设计Verilog使用FPGA

- 完成小脚丫FPGA核心板上的最基本的功能

4.5 数字系统设计

- SPI总线、I2C总线、UART等

- 连接LCD、点阵LED、传感器等扩展板,完成综合性项目

4.6 数字、模拟综合系统设计

5. 实验

- DDS信号产生:通过小脚丫FPGA逻辑设计搭配板上10位精度、最高120Msps的高速DAC(使用WebIDE,转换速率为12Msps),可以生成最高频率达5MHz的任意波形,可以通过ADALM2000的示波器功能来查看生成波形的时域信号及频谱构成;通过ADALM2000的数字IO观察送往DAC的数据总线上的数据以及DAC的时钟信号,以及这些数据和时钟之间的时序关系。涉及到的知识点:

- DAC的工作原理及使用

- 使用运放做差分转单端信号

- 模拟开关的作用

- 通过DAC的基准电压调节来调节模拟信号的幅度以及DAC对基准电压变化范围的要求

- 低通滤波器:在本系统中使用了2种低通滤波器 - 5阶巴特沃斯滤波器和5阶椭圆滤波器,截止频率为5MHz。可以通过ADALM2000的网络分析功能来对比这两种滤波器的幅频特性和相频特性,以及二者之间的优缺点、使用场景的不同等,通过LTSpice仿真软件和实际的测试来了解高频无源滤波器的构成以及性能,并对比实际测试分析理论分析和实际实现之间的差异,理解阻抗匹配在射频电路中的作用,涉及到的知识点:

- 模拟滤波器的设计及基本概念

- 使用滤波器设计软件来设计滤波器的结构及参数

- 使用仿真软件LTSpice来分析滤波器的特性

- 滤波器的幅频特性和相频特性

- 使用网络分析来测量和分析滤波器的特性

- 高频、宽带、轨到轨运算放大器的信号放大以及直流偏移的调节。可以通过ADALM2000的信号发生器来注入模拟信号、直流可调电压提供直流偏移、并使用示波器功能来观察运算放大器的输出功能,使用ADALM2000的频谱分析功能观察放大器的失真、噪声来源等。涉及到的知识点

- 轨到轨运算放大器的使用

- 宽带放大器的增益设置

- 带宽和压摆率的关系。

- 基准电压的产生和利用

- 采用比较器 + FPGA逻辑制作的Sigma Delta ADC

- 高速ADC数据采集

- 模拟信号的程控衰减、增益

- 升压型开关稳压器

- 降压型开关稳压器

- 线性稳压/LDO稳压器

- 电荷泵/负电压生成

6. 开机测试

使用Lattice XO2-4000HC FPGA小脚丫,下载测试程序:模拟信号训练学习平台FPGA代码,解压后生成jed文件可以下载。

连接方式见图片:

板上的跳线除以下的跳线不连接之外,其它都连接:

- 用于扩展测试的管脚信号:

- J4的Vb - 对外提供5V直流电压,跳线两端都连接J2安装的FPGA核心板的+5V供电电压,用于对外供电

- J4的X1 - 对外提供一个IO,跳线两端都连接J2安装的FPGA的IO39,用于对外提供数字接口信号

- J4的GND - 对外提供GND,跳线两端都已经接地

- J5的3.3V - 对外提供3.3V直流电压,跳线两端都已经连接在J2安装的FPGA核心板的3.3V上

- J5的X2 - 对外提供一个IO,跳线两端都连接J2安装的FPGA的IO2,用于对外提供数字接口信号

- J5的GND - 对外提供GND,跳线两端都已经接地

- 用于信号输入的管脚信号

- J7 - 用于模拟信号输入,左侧为用Sigma Delta测试的模拟信号电压,右侧为GND

二选一跳线:

- JP3:连接左侧两个管脚,使得在J6上输出的信号来自高速DAC生成的模拟信号